Michael von Wenckstern

Verification of Structural and Extra-Functional Properties in Component and Connector Models for Embedded and Cyber-Physical Systems

Aachener Informatik Berichte, Software Engineering Hrsg.: Prof. Dr. B. Rumpe

Band 44

[vW20] M. von Wenckstern: Verification of Structural and Extra Functional Properties in Component and Connector Models for Embedded and Cyber Physical Systems. Shaker Verlag, ISBN 978-3-8440-7239-6. Aachener Informatik-Berichte, Software Engineering, Band 44. March 2018. www.se-rwth.de/publications/

## Verification of Structural and Extra-Functional Properties in Component and Connector Models for Embedded and Cyber-Physical Systems

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der RWTH Aachen University zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

## Dipl.-Math. Michael von Wenckstern aus Karl-Marx-Stadt

Berichter: Universitätsprofessor Dr. rer. nat. Bernhard Rumpe University Professor Shahar Maoz, PhD

Tag der mündlichen Prüfung: 31.10.2019

## Abstract

The industry area of embedded and cyber-physical systems is one of the largest and it influences our daily life. The global embedded systems marked was valued at about 160 billion US dollar in 2015 and it is getting up to 225 billion US dollar by end of 2021 [Zio17]. Example domains of embedded and cyber-physical systems are: automotive [DHJ<sup>+</sup>08], avionics [FLV03], robotics [WICE03], railway [DNCH10], production industry [EWSG94], telecommunication [ZSM11], healthcare [ERA09], defense [BNP<sup>+</sup>04], and consumer electronics [VOVDLKM00].

Model-based engineering, esp. component and connector (C&C) models to describe logical architectures, are one common approach to handle the large complexity of embedded and cyber-physical systems [FR07, MBNJ09, OMG15, EJL<sup>+</sup>03]. Components encapsulate software features; the hierarchical decomposition of components enables formulating logical architectures in a top-down approach. Connectors in C&C models describe the information exchange via typed ports; they model black-box communication between software features.

The current development of complex C&C-based embedded systems in industry mostly involves the following steps [BMR<sup>+</sup>17a, DGH<sup>+</sup>19]: (1) formulating functional and extra-functional requirements as text in *IBM Rational DOORS*; (2) creating a design model of the software architecture including its environment interactions in *SysML*; (3) developing a complete functional/logical model to simulate the embedded system in *Simulink*; and (4) system implementation based on available hardware in C/C++ satisfying all extra-functional properties.

This current development process has the following disadvantages [KBFS12, HKK<sup>+</sup>18, BMR<sup>+</sup>17a]: (a) *SysML* models do not follow a formalized approach; i.e., engineers may interpret these models differently due to missing semantics; (b) the check between the informal *SysML* architecture design against the *Simulink* model is done manually, and thus, error-prone and very time-consuming; (c) refactoring of *Simulink* models (e.g., dividing a subsystem) needs manual effort in updating the design model, and therefore, due to timing constraints this step is often skipped resulting in inconsistencies; and (d) most tools do not support a generic approach for different extra-functional property kinds, and thus, extra-functional properties are mostly modeled as comments or stereotypes and consistencies between these properties are checked manually.

This thesis aims to improve the software development process of large and complex C&C models for embedded and cyber-physical systems by providing model-based methodologies to develop, understand, validate and maintain these C&C models. Concrete, this thesis presents concepts to support the embedded software engineer with: (i) automatic consistency checks of C&C models; (ii) automatic verification of logical C&C models against their design decisions; (iii) automatic addition of traceability links between design and implementation models; (iv) finding structural inconsistencies during model evolution; (v) providing a flexible framework to define different extra-functional property types; (vi) presenting an *OCL* framework to specify (company-specific) constraints about structural or extra-functional properties for C&C models; and (vii) generation of positive or negative witnesses to explain why a C&C model satisfies or violates its extra-functional or structural constraints or its design decisions.

Prototype implementations of above mentioned concepts and an industrial case study in cooperation with Daimler AG show promising results in improving the model-based development process of embedded and cyber-physical systems in industry.

## Acknowledgments

Special thanks goes to my doctor father Prof. Dr. Bernhard Rumpe for giving me the opportunity to research in the area of model-driven software engineering and for providing many connections to other research groups and industrial partners; participating in several research and automotive industry projects gave me access to many different views on this research topic. Furthermore, I want to express great laud to Prof. Dr. Bernhard Rumpe for the fruitful discussions, ideas and feedback rounds - especially during the 3-day long research workshops - on this thesis.

I would like to thank Prof. Shahar Maoz for being the second reporter of this thesis. Additionally, I want to express gratitude to Prof. Shahar Maoz, Dr. Jan Oliver Ringert, and Prof. Dr. Bernhard Rumpe for the successful teamwork on the GIF research project I-1235-407.6/2014, for the published papers together, and for the time together in Tel Aviv and in Aachen. I also want to thank the Deutsche Forschungsgemeinschaft (DFG) for funding this research and thus supporting this thesis.

Moreover, I would like to thank Prof. Dr. Stefan Kowalewski for heading my PhD exam committee, and Prof. Dr. Erika Ábrahám for being part of this committee.

In addition, my thank goes to Prof. Dr. Manfred Nagl for many interesting discussions about computer science, GI, and architecture.

"If everyone is moving forward together, then success takes care of itself." - Henry Ford about teamwork. Therefore, special thanks goes to Evgeny Kusmenko; together we developed the EmbeddedMontiArc modeling family and had good times on several conferences and workshops presenting our papers. Moreover, I want to thank Dr. Pedram Mir Seyed Nazari for the interesting discussions about language engineering and digitalization; for the first level MontiCore support thanks goes to Pedram, Marita Breuer, and Galina Volkova. Additionally, I want to thank Dr. Alexander Roth, Dr. Christoph Schulz, and Vincent Bertram for the many papers we wrote together. I want to thank Deni Raco for organizing all the extra activities such as poker, or soccer events on our chair.

I also would like to thank the students whose bachelor or master theses supported my research significantly; without them the large evaluation part would not be possible. Thanks goes to "Web(Assembly) expert" Jean-Marc Ronck, "OCL specialist" Ferdinand Mehlan, "C++ generator enthusiast" Sascha Schneiders, and "tooling and gaming fan" Malte Heithoff for supporting me more than two years.

I want to extend my thanks to the other students: Luca Tabone, Stefan Brunecker, Alexander Kogaj, Nicolai Strodthoff, Severin Tolksdorf, Vladimir Parashin, David Ernst, Christian Bajana, Igor Shumeiko, Dinh-An Ho, Fabian Kahlert, Manuel Schrick, Ievgen Strepkov, Ahmet Tayfun Özen, and all seminar and lab students.

Special thanks for reviewing this PhD thesis goes to Sebastian von Wenckstern, Pedram Mir Seyed Nazari, Evgeny Kusmenko, Kai Adam, Simon Varga, and Oliver Kautz.

Furthermore, I would like to thank all colleges of the Software Engineering chair for the nice time together: Lennart Bucher, Arvid Butting, Manuela Dalibor, Anabel Derlam, Florian Donath, Imke Drave, Robert Eikermann, Dr. Timo Greifenberg, Sylvia Gunder, Dr. Arne Haber, Dr. Lars Hermerschmidt, Dr. Christoph Herrmann, Gabriele Heuschen, Steffen Hillemacher, Dr. Katrin Hölldobler, Carsten Kolassa, Thomas Kurpick, Achim Lindt, Dr. Markus Look, Matthias Markthaler, Dr. Judith Michael, Dr. Klaus Müller, Sonja Müßigbrodt, Lukas Netz, Jerome Pfeiffer, Nina Pichler, Dimitri Plotnikov, Manuel Putzer, Dr. Dirk Reiß, David Schmalzing, Stephanie Schrader, Brian Sinkovec, Max Voß, Louis Wachtmeister, and Dr. Andreas Wortmann.

My largest thanks goes to my family - Bettina, Bodo, and Sebastian von Wenckstern - who supported me all these years; and their belief that education is the best investment for my future.

Aschaffenburg, 13.12.2019 Michael von Wenckstern

# Contents

| 1. | Intro | Introduction |                                                                    |    |  |

|----|-------|--------------|--------------------------------------------------------------------|----|--|

|    | 1.1.  | Contex       | tt and Foundations                                                 | 2  |  |

|    |       | 1.1.1.       | Component and Connector Models and their Specification Language    | 3  |  |

|    |       | 1.1.2.       | Model Based Systems Engineering                                    | 5  |  |

|    |       | 1.1.3.       |                                                                    | 9  |  |

|    | 1.2.  | Requir       | ements on PhD Thesis                                               | 13 |  |

|    |       | 1.2.1.       | Enhancing the C&C Views Language                                   | 13 |  |

|    |       | 1.2.2.       | 8                                                                  | 13 |  |

|    |       | 1.2.3.       | Integrating C&C Views in the Development Process and Environment . | 14 |  |

|    |       | 1.2.4.       | Evaluation                                                         | 14 |  |

|    |       | 1.2.5.       | Further Remarks                                                    | 14 |  |

|    | 1.3.  |              | ive and Main Results                                               | 15 |  |

|    | 1.4.  |              | Organization                                                       | 17 |  |

|    | 1.5.  | Publica      | ations                                                             | 17 |  |

| 2. | Und   | erlying      | g Development Methodology                                          | 21 |  |

|    | 2.1.  | System       | s Engineering Process at Daimler AG                                | 21 |  |

|    |       | 2.1.1.       | Current Development Process at Daimler AG                          | 21 |  |

|    |       | 2.1.2.       | Improving the Development Process at Daimler AG                    | 23 |  |

|    |       |              | izing the Systems Engineering Process using SMARDT                 | 27 |  |

|    |       | 2.2.1.       | Current Systems Engineering Process at BMW Group                   | 27 |  |

|    |       | 2.2.2.       | Overview of SMARDT process                                         | 28 |  |

|    |       |              | r Existing Methodologies and Model-based Approaches                | 33 |  |

|    |       | 2.3.1.       | Simulink Requirements                                              | 34 |  |

|    |       | 2.3.2.       | Mentor Capital                                                     | 35 |  |

|    |       | 2.3.3.       | Polarsys Arcadia                                                   | 36 |  |

|    |       | 2.3.4.       | Vector PREEvision                                                  | 38 |  |

| 3. | Con   | crete S      | Syntax of EmbeddedMontiArc                                         | 41 |  |

|    | 3.1.  |              | ements for a Logical Architecture Modeling Language                | 42 |  |

|    | 3.2.  | Existin      | g C&C Modeling Languages                                           | 43 |  |

|    | 3.3.  |              | arison to Other <i>MontiArc</i> Derivatives                        | 49 |  |

|    | 3.4.  | *            |                                                                    | 54 |  |

|    | 3.5.  |              |                                                                    |    |  |

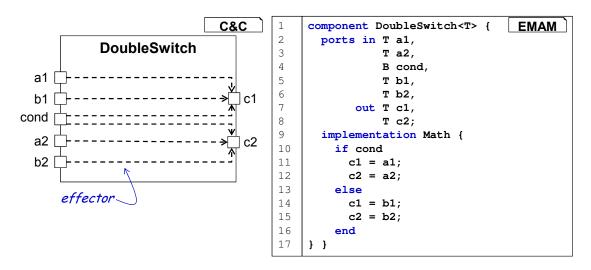

|    |       | 3.5.1.       |                                                                    | 62 |  |

|    |       | 3.5.2.       |                                                                    | 64 |  |

|    |       | 3.5.3.       |                                                                    | 65 |  |

|    |            | 3.5.4. Type Parameters                                                        | 66  |

|----|------------|-------------------------------------------------------------------------------|-----|

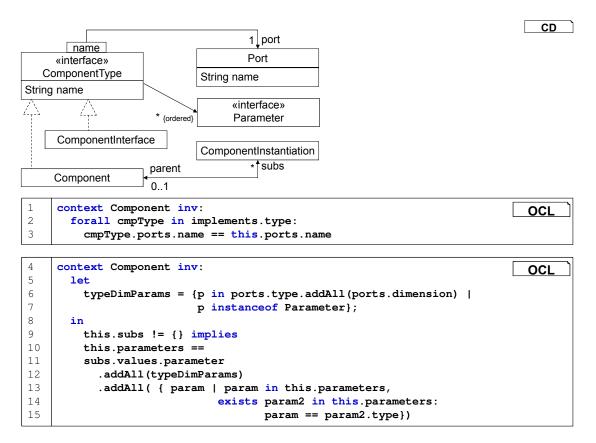

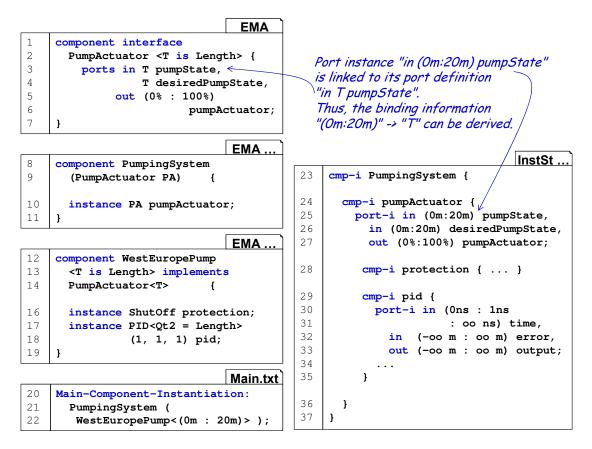

|    | 3.6.       | Components and Ports in <i>EmbeddedMontiArc</i>                               | 70  |

|    |            | 3.6.1. Component Type Definitions and Component Instantiations                | 70  |

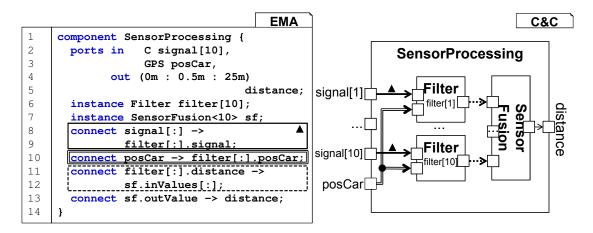

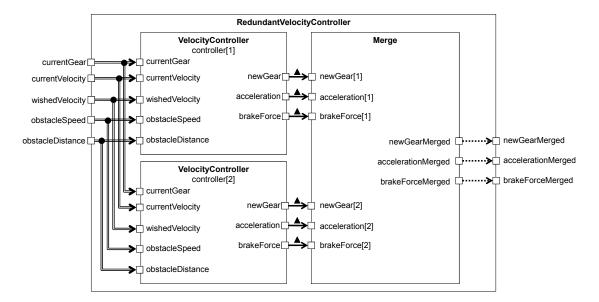

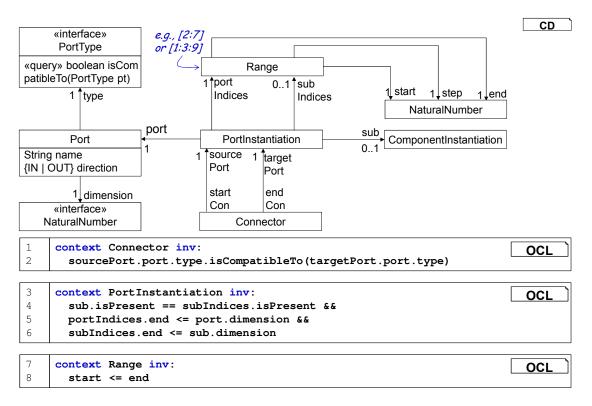

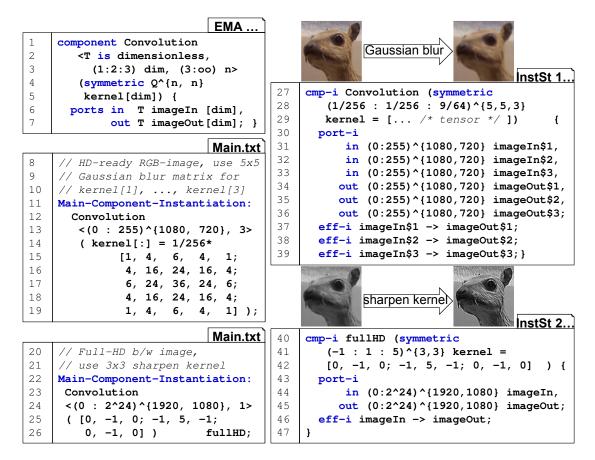

|    |            | 3.6.2. Arrays of Ports and Component Instantiations                           | 72  |

|    |            | 3.6.3. Component Interfaces                                                   | 73  |

|    |            | 3.6.4. Reference Architectures with Configuration Parameters                  | 74  |

|    |            | 3.6.5. Product-Line Modeling with Configuration Parameters and Default Values | 78  |

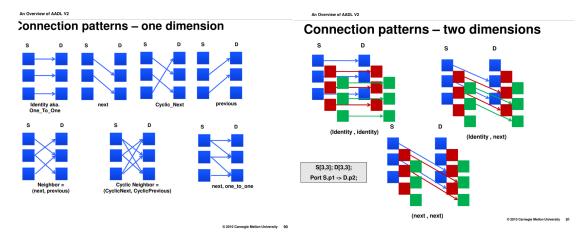

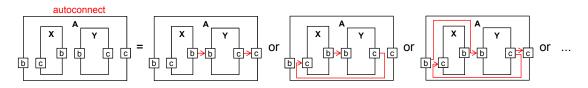

|    |            | 3.6.6. Connections                                                            | 83  |

|    |            | 3.6.7. Main Component Instantiation and Packaging                             | 88  |

|    |            | 3.6.8. Arrays of Component Types, Generic and Configuration Parameters        | 90  |

|    | 3.7.       | Concepts of New Language Features                                             | 92  |

|    | 3.8.       | Example Use Case for <i>EmbeddedMontiArc</i> in Business Domain               | 95  |

|    | 3.9.       | EmbeddedMontiArcStudio: Tooling for Users                                     | 96  |

|    |            |                                                                               |     |

| 4. |            | •                                                                             | 03  |

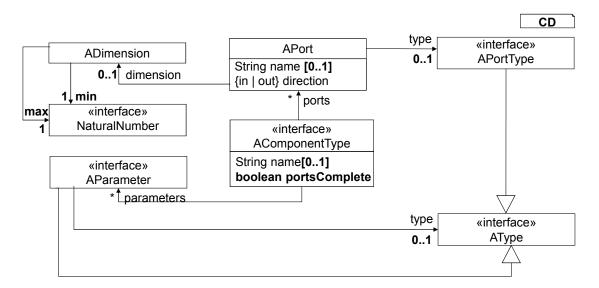

|    |            | e e                                                                           | 04  |

|    | 4.2.       | 1                                                                             | 07  |

|    |            |                                                                               | 08  |

|    |            | 0                                                                             | 11  |

|    |            | 1 A A A A A A A A A A A A A A A A A A A                                       | 15  |

|    |            | 4.2.4. Ports and Connectors                                                   | 16  |

|    |            |                                                                               | 19  |

|    |            |                                                                               | 20  |

|    |            | 1                                                                             | 21  |

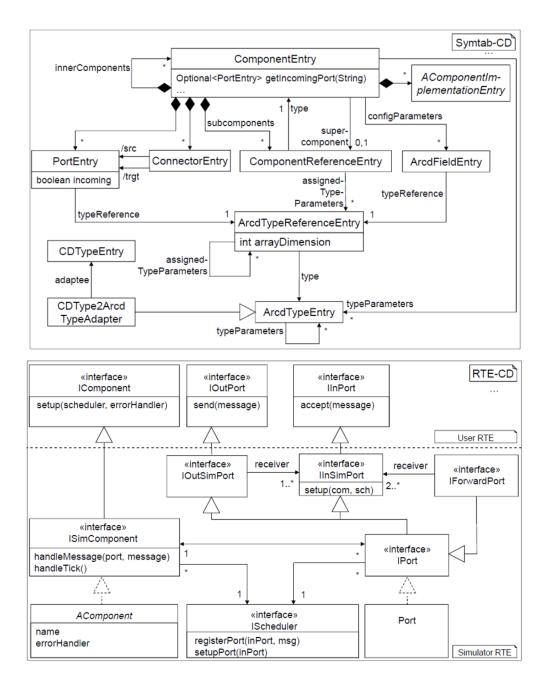

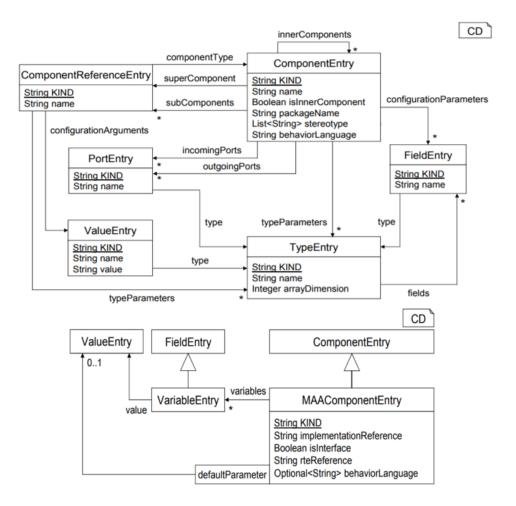

|    | 4.3.       | 1                                                                             | 22  |

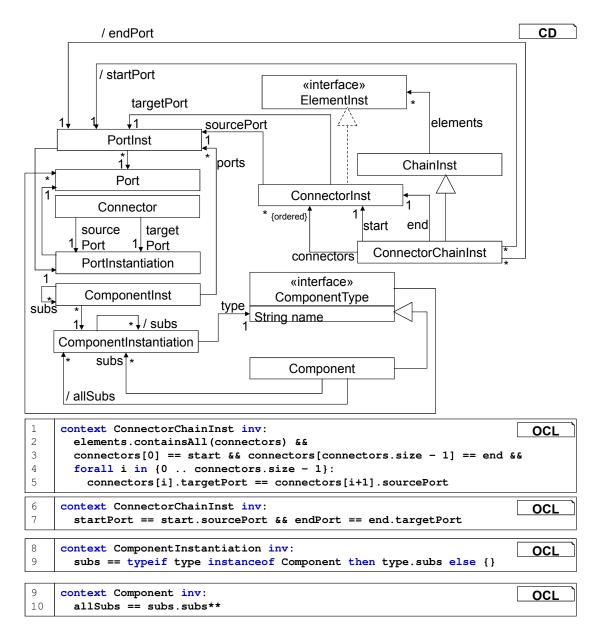

|    | 4.4.       | Derivation of C&C Instance Structure from C&C Model 1                         | 24  |

|    | 4.5.       | Comparison of <i>EmbeddedMontiArc</i> against <i>MontiArc</i> Derivatives 1   | 29  |

|    | 4.6.       | Realization of the Abstract Syntax with Symbol Management Infrastructure 1    | 37  |

| _  | <b>-</b> . |                                                                               |     |

| 5. |            | <b>3</b>                                                                      | 45  |

|    | 5.1.       |                                                                               | 46  |

|    | 5.2.       |                                                                               | 48  |

|    |            | 1 5                                                                           | 53  |

|    |            |                                                                               | 54  |

|    | 5.5.       |                                                                               | 57  |

|    |            |                                                                               | 58  |

|    |            | 6                                                                             | 59  |

|    |            | 6                                                                             | 61  |

|    |            |                                                                               | 65  |

|    |            | 5.5.5. Consistency Rules between Tag Model and Tag Schema                     | 67  |

| 6. | oci        | L Framework to Describe Structural and Extra-Functional Properties 1          | 69  |

|    |            | •                                                                             | 70  |

|    | ~          |                                                                               | 70  |

|    |            |                                                                               | . 0 |

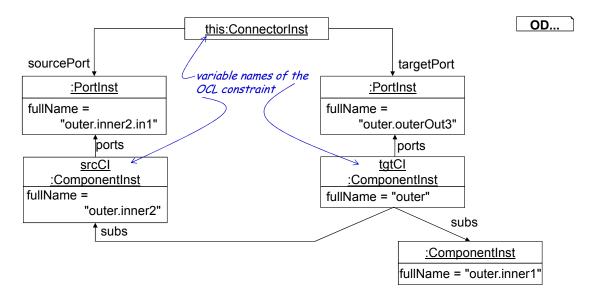

|    |                                                            | 6.1.2. CO1: Connectors May Not Pierce Through Component Interface                       |                                                                    | 171 |

|----|------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----|

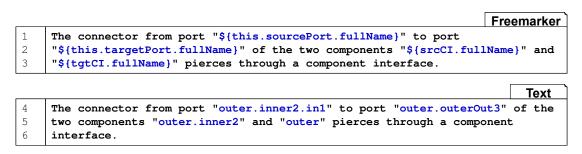

|    |                                                            | 6.1.3. R1/R2:Connection Rules for Outgoing and Incoming Ports .                         |                                                                    | 174 |

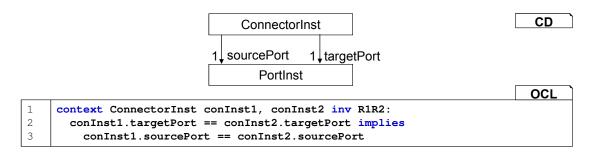

|    |                                                            | 6.1.4. R13: No Subcomponent Instantiation Cycles                                        |                                                                    | 175 |

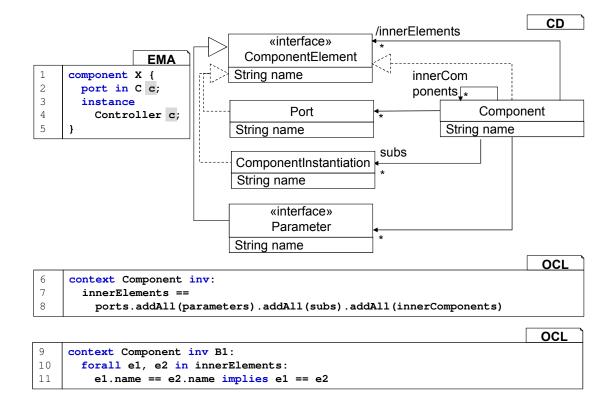

|    |                                                            | 6.1.5.                                                                                  | B1: Names Are Unique Within Component Namespace                    | 176 |

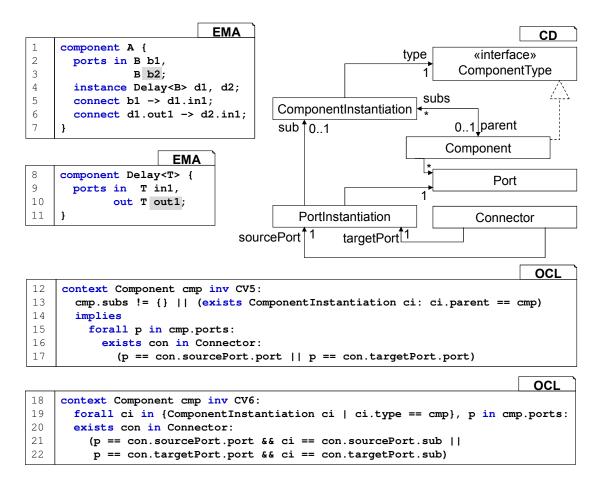

|    |                                                            | 6.1.6.                                                                                  | CV5/CV6: All Ports Should Be Used Once                             | 177 |

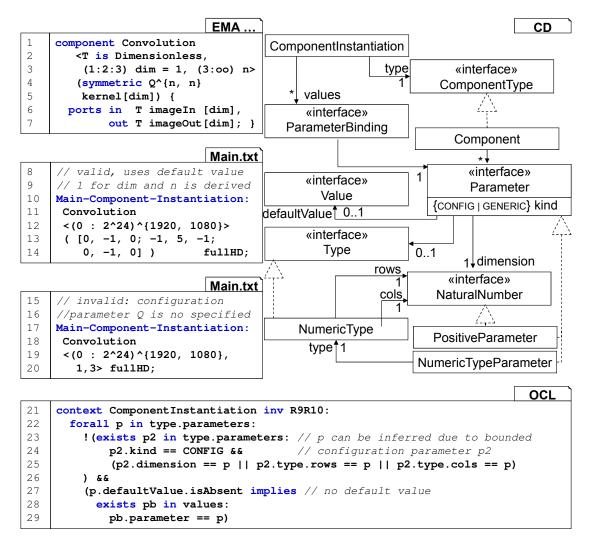

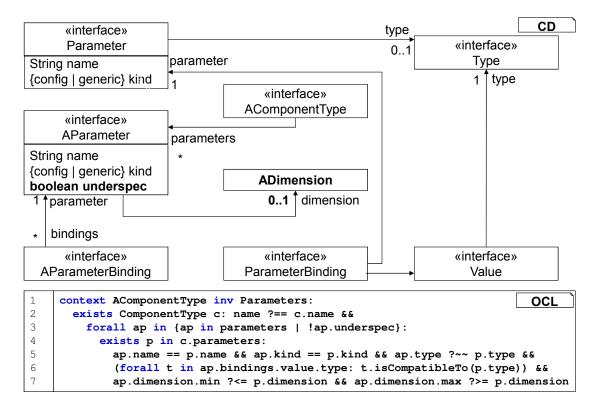

|    |                                                            | 6.1.7.                                                                                  | R9/R10: All Parameters Must be Bound During Instantiation          | 179 |

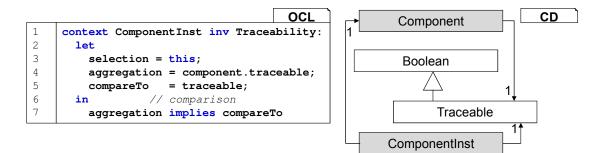

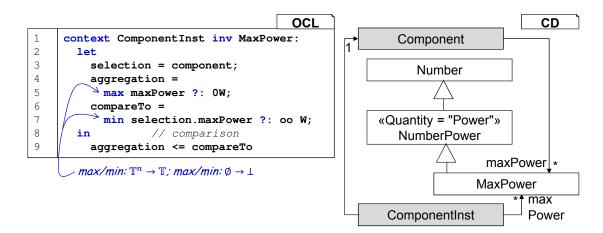

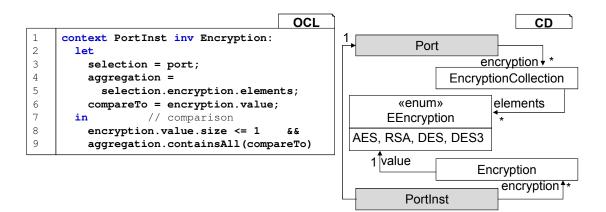

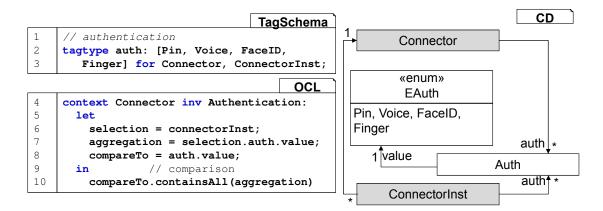

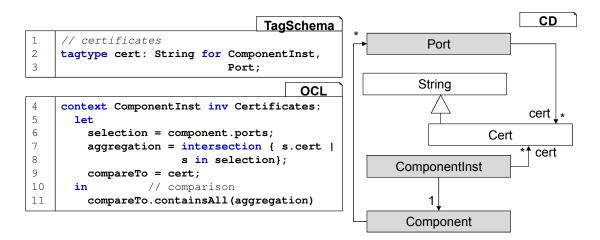

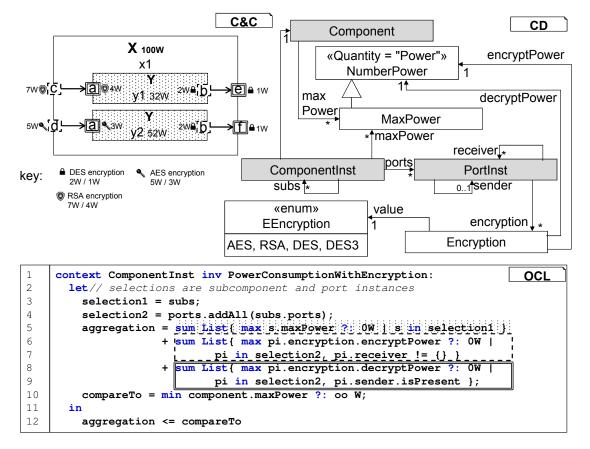

|    | 6.2.                                                       | Definin                                                                                 | g Extra-Functional Properties in OCL                               | 182 |

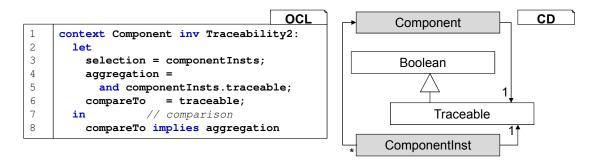

|    |                                                            | 6.2.1.                                                                                  | Traceability for Component Instantiation                           | 182 |

|    |                                                            | 6.2.2.                                                                                  | Maximal Power Consumption for Component Instantiation              | 183 |

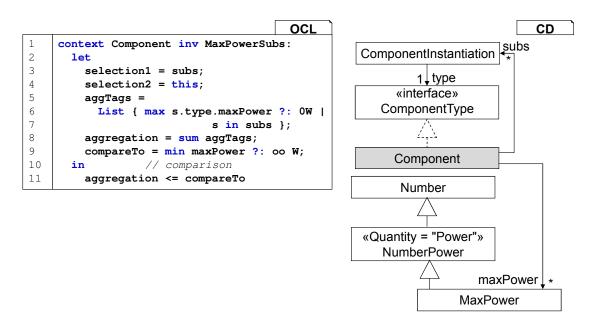

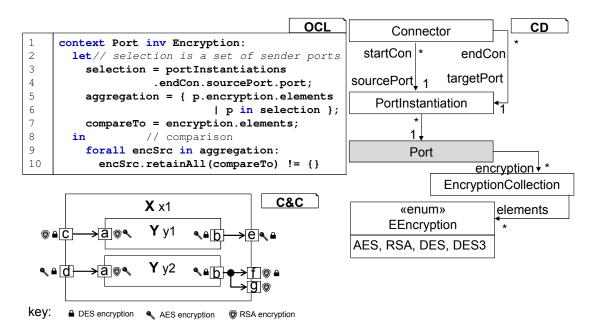

|    |                                                            | 6.2.3.                                                                                  | Encryption for Port Instantiation                                  | 184 |

|    |                                                            | 6.2.4.                                                                                  | Authentication for Connector Instantiation                         | 185 |

|    |                                                            | 6.2.5. Certificates for Component Instances/Port Definitions                            |                                                                    | 186 |

|    |                                                            | 6.2.6. Maximal Power Consumption of Subcomponent Instantiations .                       |                                                                    | 187 |

|    | · ·                                                        |                                                                                         | Encryption for Target Ports                                        | 188 |

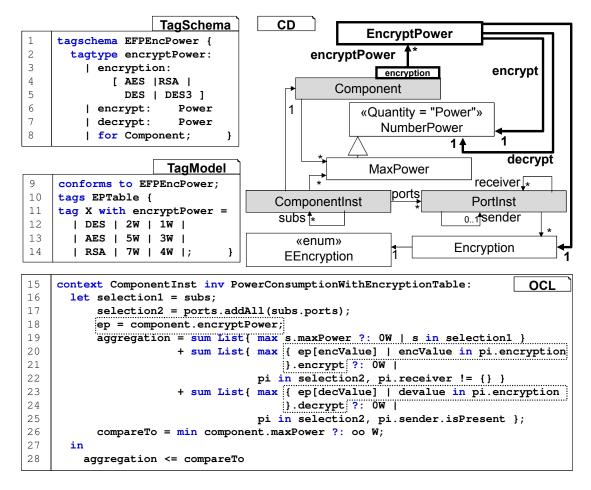

|    | 6.2.8. Power Consumption Considering Encryption            |                                                                                         | Power Consumption Considering Encryption                           | 189 |

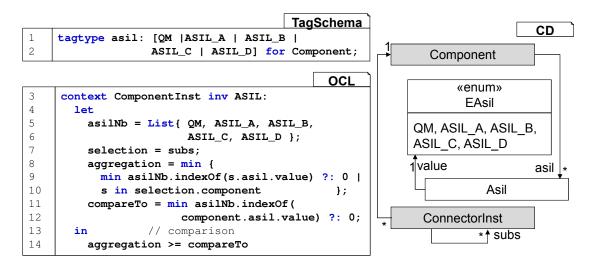

|    |                                                            | 6.2.9.                                                                                  | Automotive Safety Integrity Level for Component Definitions        | 192 |

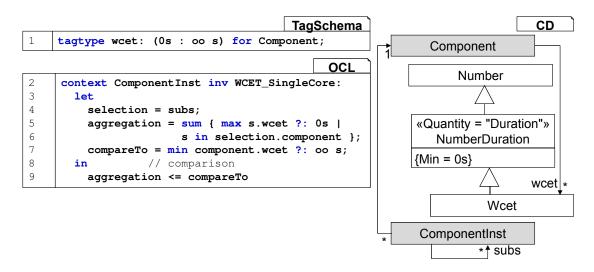

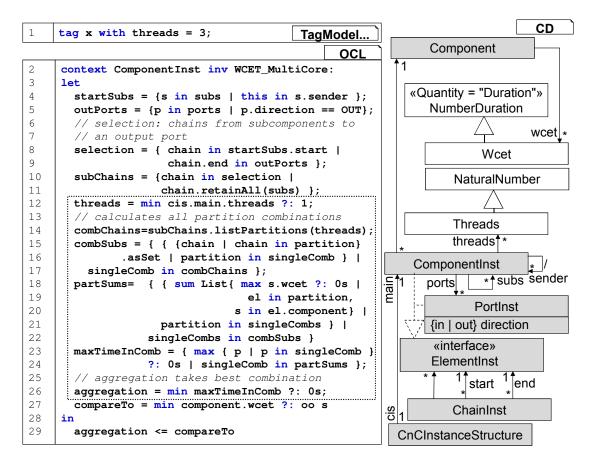

|    |                                                            | 6.2.10.                                                                                 | Worst Case Execution Time for Single Core Processors               | 193 |

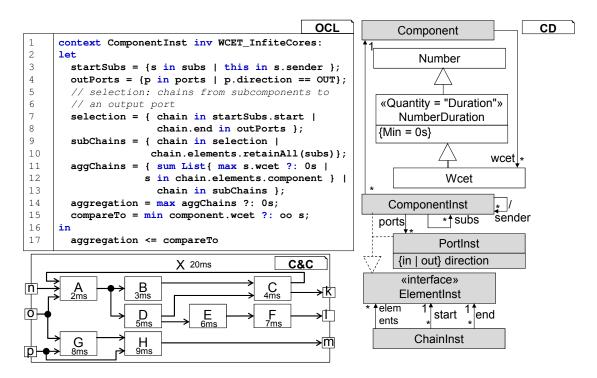

|    |                                                            | 6.2.11.                                                                                 | Worst Case Execution Time for Processors with Infinite Cores       | 193 |

|    |                                                            | 6.2.12.                                                                                 | Worst Case Execution Time for Multi Thread Processors              | 195 |

|    | 6.3.                                                       |                                                                                         | ses of OCL Constraints for Extra-Functional Properties             | 197 |

|    |                                                            | 6.3.1.                                                                                  | Positive Consistency Witnesses                                     | 197 |

|    |                                                            | 6.3.2.                                                                                  | Negative Inconsistency Witnesses                                   | 199 |

|    | 6.4.                                                       |                                                                                         | Specify Transformations between Abstract Syntax of Two Languages . | 201 |

|    | 6.5.                                                       | 1                                                                                       |                                                                    | 207 |

|    | 6.6.                                                       | Related                                                                                 | Approaches to Constrain Structure of Architectures                 | 210 |

| 7. | 7. EmbeddedMontiView: A High-Level Design Language         |                                                                                         | MontiView: A High-Level Design Language                            | 213 |

|    | 7.1.                                                       | 1. Requirements/Features on the C&C View Language                                       |                                                                    | 214 |

|    | 7.2.                                                       | Related                                                                                 | Concepts for Verifying Component and Connector Models              | 216 |

|    | 7.3. Concrete and Abstract Syntax of EmbeddedMontiView Lan |                                                                                         | te and Abstract Syntax of <i>EmbeddedMontiView</i> Language        | 221 |

|    |                                                            |                                                                                         | 1 71                                                               |     |

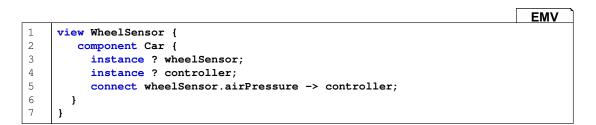

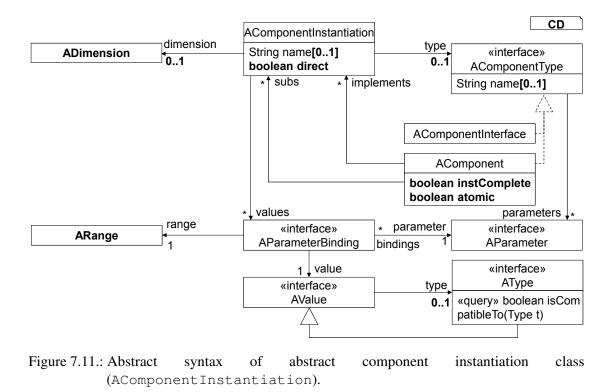

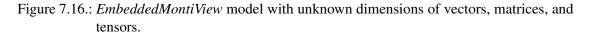

|    |                                                            | 7.3.2.                                                                                  | Abstract Component Instantiations                                  | 224 |

|    |                                                            | 7.3.3.                                                                                  | Array of Abstract Component Instances and Abstract Ports           | 224 |

|    |                                                            | 7.3.4.                                                                                  | Completeness of Abstract Component Instances                       | 226 |

|    |                                                            | 7.3.5.                                                                                  | Abstract Type Parameters                                           | 228 |

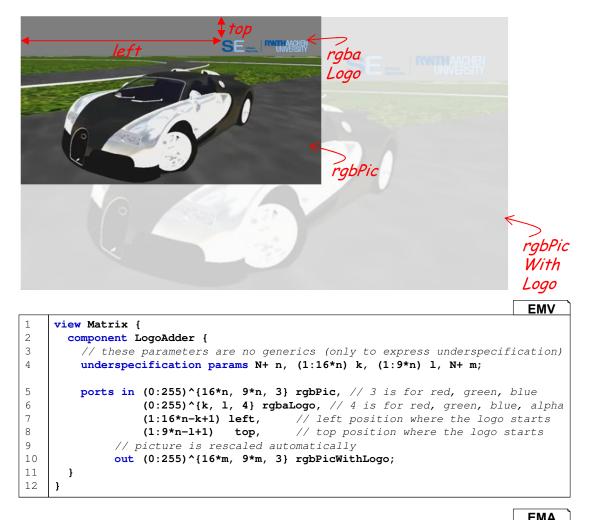

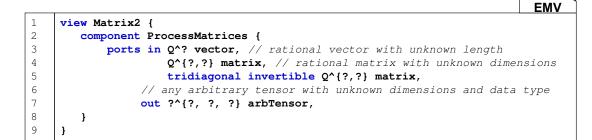

|    |                                                            | 7.3.6.                                                                                  | Matrices as Abstract Port Types                                    | 229 |

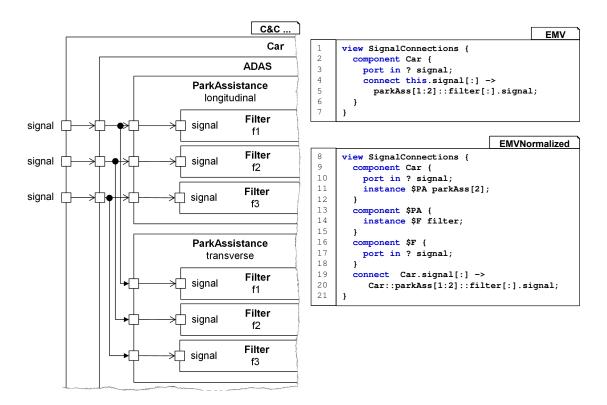

|    |                                                            | 7.3.7.                                                                                  | Abstract Connections                                               | 232 |

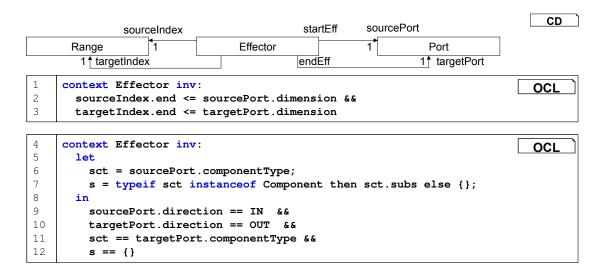

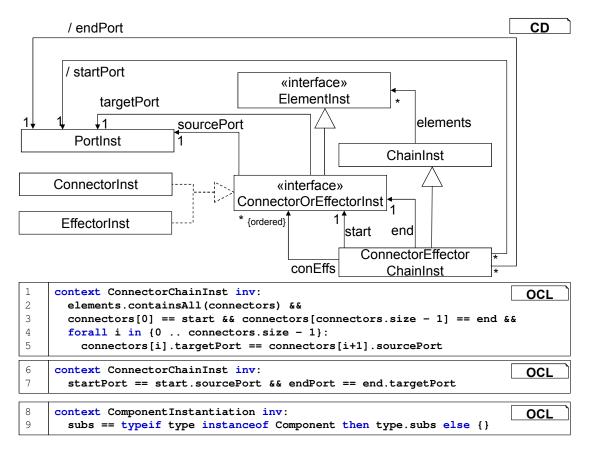

|    |                                                            | 7.3.8.                                                                                  | Abstract Effectors                                                 | 234 |

|    |                                                            | 7.3.9.                                                                                  | Imports and Full-Qualified Names                                   | 235 |

|    |                                                            |                                                                                         | Component and Connector View                                       | 236 |

|    |                                                            | 7.3.11. Some Remarks                                                                    |                                                                    | 237 |

|    | 7.4.                                                       | 4. Satisfaction Relation between <i>EmbeddedMontiView</i> and <i>EmbeddedMontiArc</i> . |                                                                    | 237 |

|    |                                                            | 7.4.1.                                                                                  | Abstract Ports                                                     | 237 |

|    |       | 7.4.2. Abstract Subcomponent Instantiations                                  | 240 |

|----|-------|------------------------------------------------------------------------------|-----|

|    |       | 7.4.3. Abstract Type Parameters                                              | 240 |

|    |       | 7.4.4. Abstract Tensors as Port Types                                        | 241 |

|    |       | 7.4.5. Abstract Connections                                                  | 242 |

|    |       | 7.4.6. Abstract Effectors                                                    | 247 |

|    |       | 7.4.7. Some Remarks                                                          | 247 |

|    | 7.5.  | Witnesses Based on Satisfaction-Relation                                     | 250 |

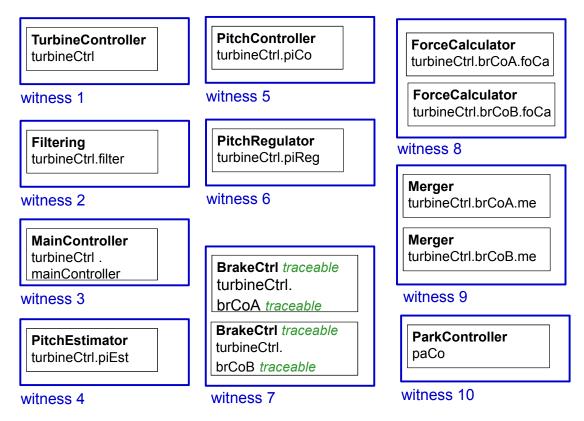

|    |       | 7.5.1. Satisfaction Witnesses                                                | 250 |

|    |       | 7.5.2. Tracing Witnesses                                                     | 262 |

|    |       | 7.5.3. Non-Satisfaction Witnesses                                            | 265 |

|    |       |                                                                              |     |

| 8. | Indu  | Istrial Case Study on Component and Connector Views                          | 269 |

|    | 8.1.  |                                                                              | 269 |

|    | 8.2.  |                                                                              | 271 |

|    |       | 8.2.1. Execution of Preliminary Study                                        | 271 |

|    |       | 8.2.2. Results of Preliminary Study                                          | 272 |

|    | 8.3.  | Main Study                                                                   | 279 |

|    |       | 8.3.1. Addressing Traceability                                               | 282 |

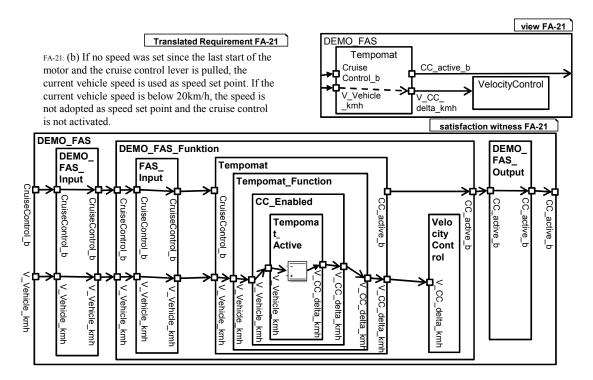

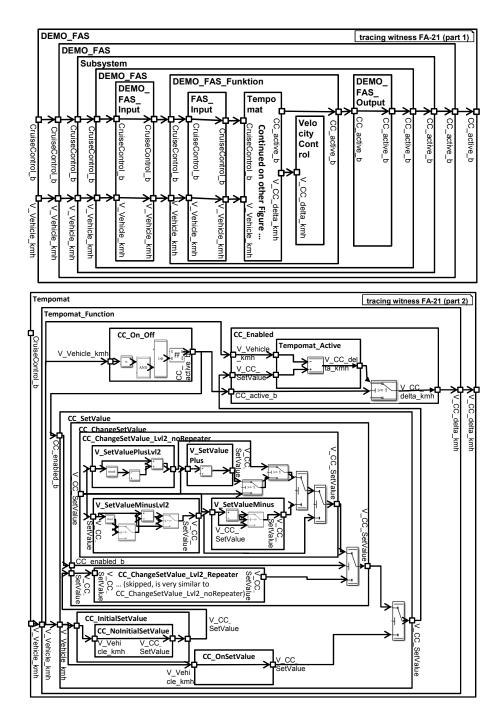

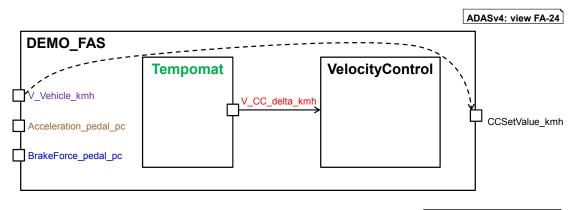

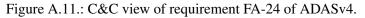

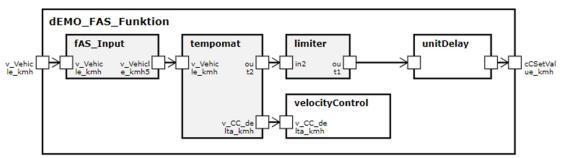

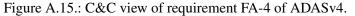

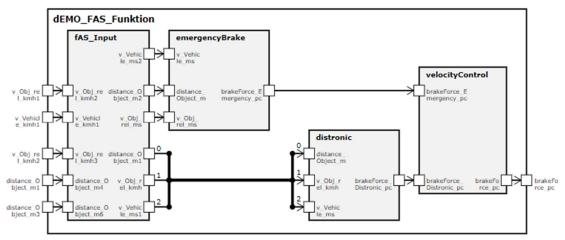

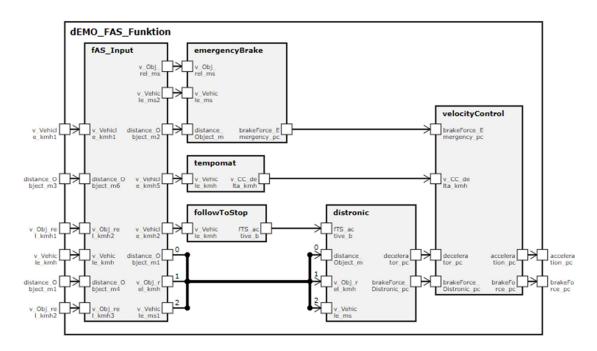

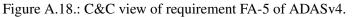

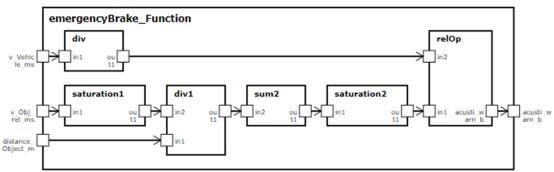

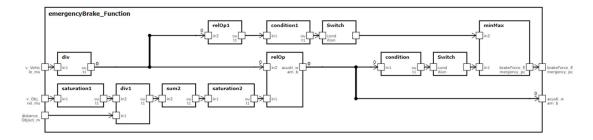

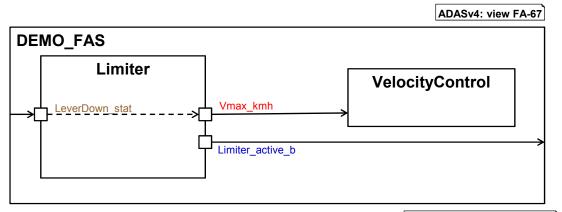

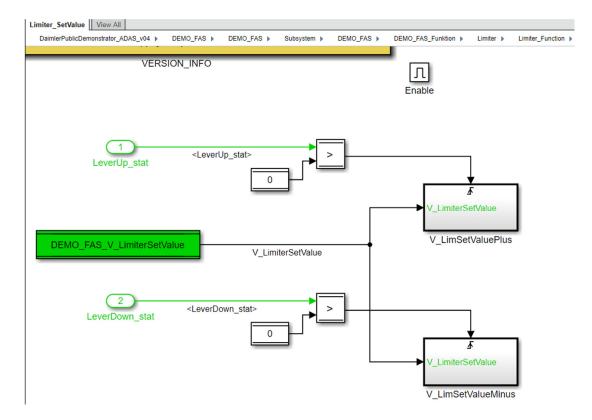

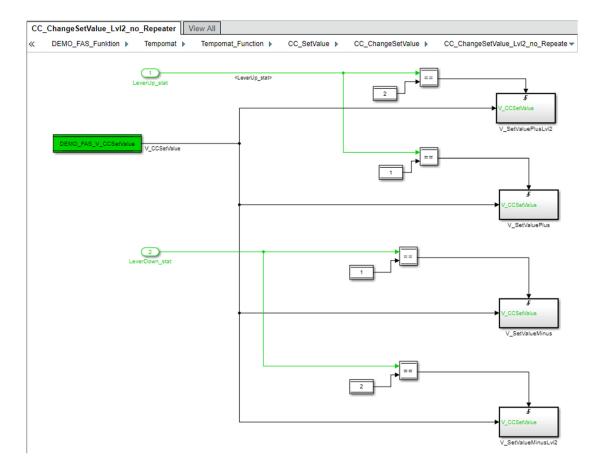

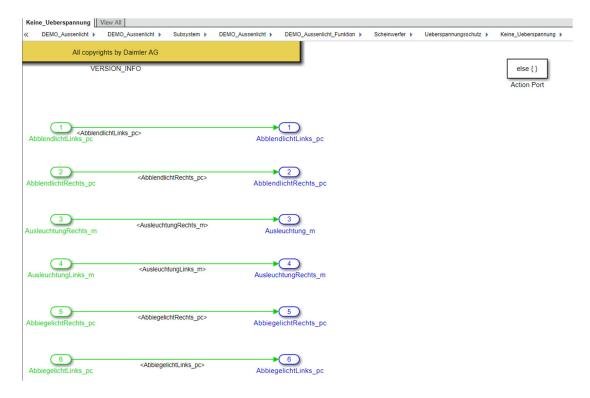

|    |       | 8.3.2. Example of a Requirement, C&C View, and Graphical Witness             | 283 |

|    |       | 8.3.3. Design Decisions for Creating C&C Views                               | 286 |

|    |       | 8.3.4. Addressing Evolution                                                  | 286 |

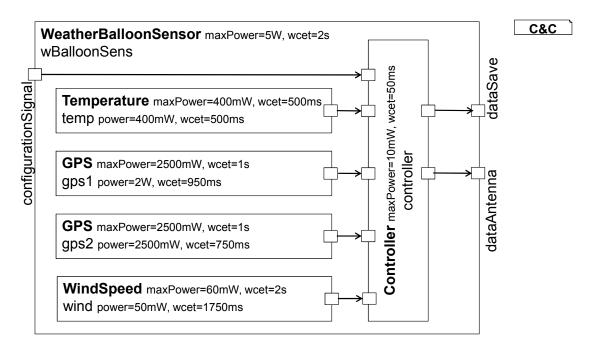

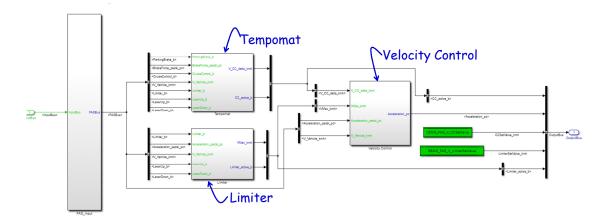

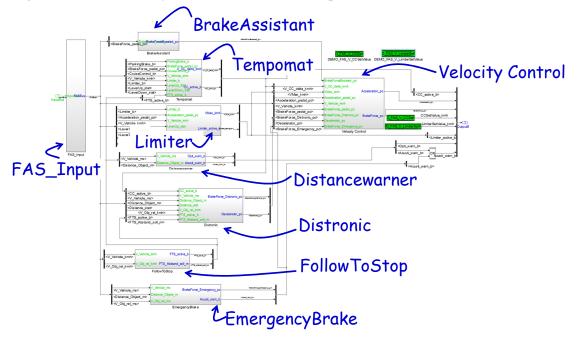

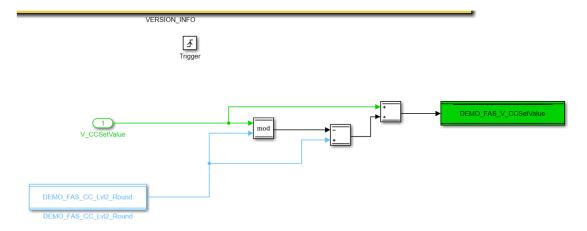

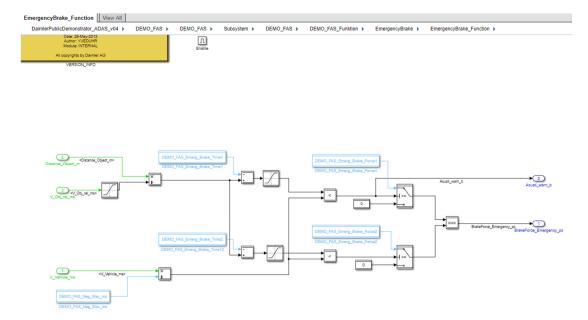

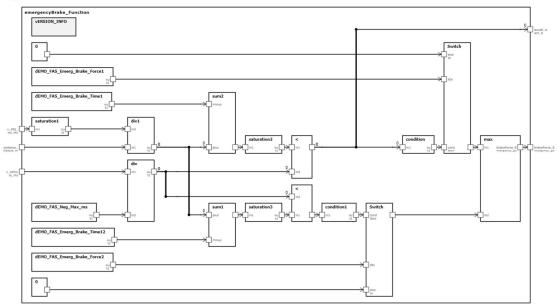

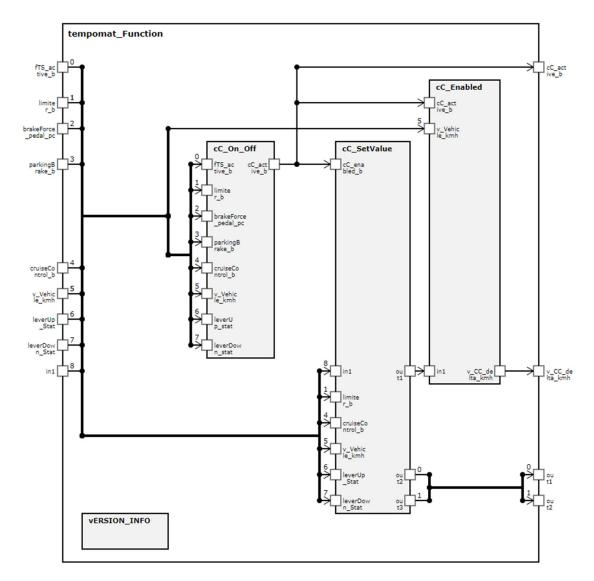

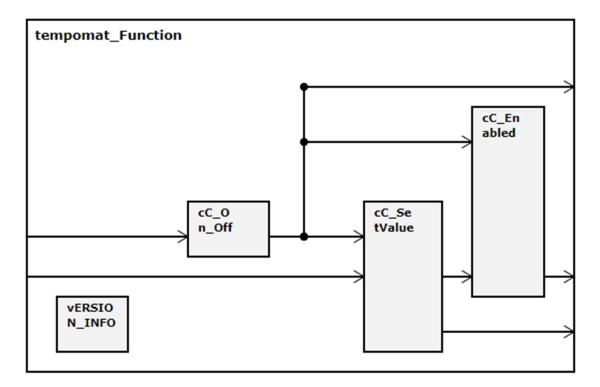

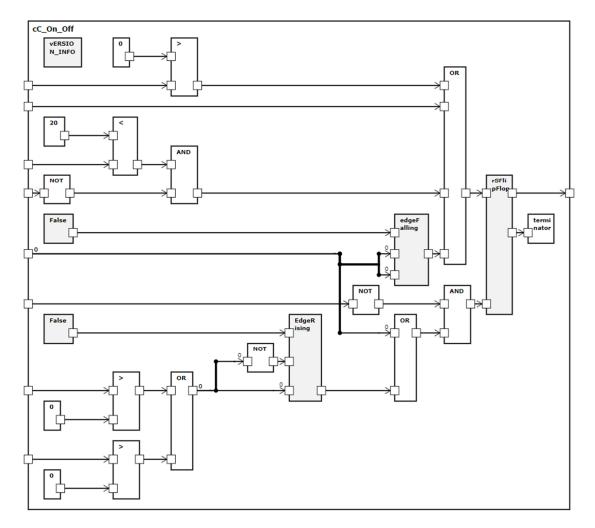

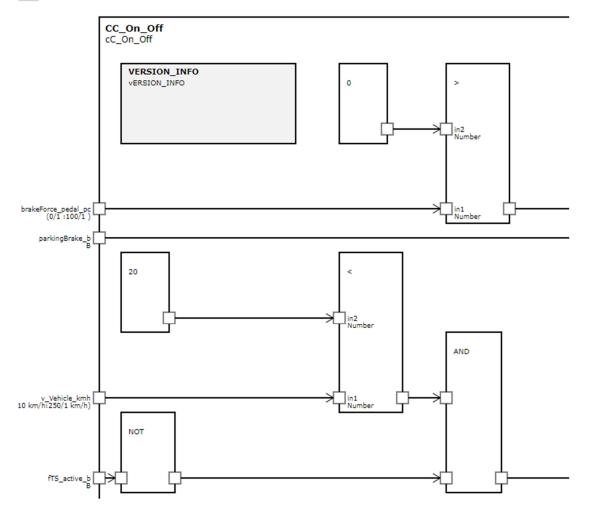

|    |       | 8.3.5. Translating <i>Simulink</i> Block Diagrams to <i>EmbeddedMontiArc</i> | 288 |

|    | 8.4.  | Results of Main Study                                                        | 292 |

|    |       | 8.4.1. Feasibility and Effort to Create C&C Views                            | 292 |

|    |       | 8.4.2. Technical Applicability                                               | 294 |

|    |       | 8.4.3. Helpfulness of Witnesses                                              | 296 |

|    |       | 8.4.4. Results from Addressing the Identified Challenges                     | 298 |

|    | 8.5.  | Subsequent Study                                                             | 299 |

|    |       | 8.5.1. Generation of Graphical Representations of C&C Models and Witnesses   | 300 |

|    |       | 8.5.2. Results of Subsequent Study                                           | 306 |

|    | 8.6.  | Additional Observations and Desired Extensions                               | 308 |

|    | 8.7.  | Threats to Validity                                                          | 310 |

|    | 8.8.  | Similar Studies                                                              | 310 |

|    | 8.9.  | Summary of Industrial Case Study                                             | 311 |

|    | _     |                                                                              |     |

| 9. |       | mary and Conclusion                                                          | 313 |

|    |       | Main Results                                                                 | 313 |

|    | 9.2.  | Conclusion                                                                   | 315 |

| Δ  | Δnn   | endix for Industrial Case Study                                              | 317 |

| Π. |       | Screenshots of Visualisation                                                 | 317 |

|    |       | Screenshots of Graphical Representation of C&C Views and Witnesses           | 325 |

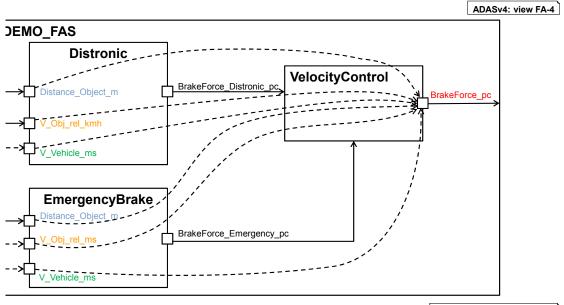

|    | 11.4. | A.2.1. FA-24                                                                 | 325 |

|    |       | A.2.1. FA-24                                                                 |     |

|    |       | 11.4.4. 111-7                                                                | 520 |

|                                                         |                                                                                                                                                              | Identified Errors during Case St<br>A.3.1. ADAS | f Verification Tool | 332<br>332 |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------|------------|

| В.                                                      | Clas                                                                                                                                                         | s Diagram in CD4A Syntax                        |                     | 349        |

| C.                                                      | C. Other Material         C.1. MontiCore 5 grammar for C&C instance structure         C.2. Operator Priority in OCL         C.3. Material to Chain Instances |                                                 |                     |            |

| Bił                                                     | Bibliography                                                                                                                                                 |                                                 |                     |            |

| Lis                                                     | List of Figures                                                                                                                                              |                                                 |                     | 427        |

| Lis                                                     | List of Tables                                                                                                                                               |                                                 |                     |            |

| Cu                                                      | Curriculum Vitae                                                                                                                                             |                                                 |                     |            |

| Related Interesting Work from the SE Group, RWTH Aachen |                                                                                                                                                              |                                                 |                     | 443        |

# Chapter 1. Introduction

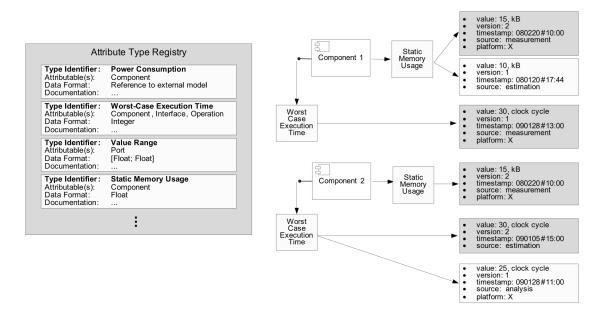

Modern software systems are becoming more and more complex in many areas [FR07, PBKS07, FB11, Bro05]. One prominent area for complex software and software-intensive systems is the field of embedded and cyber-physical systems [Lee08]. Engineering cyber-physical systems rises specific challenges that are rarely present in other software engineering disciplines due to the systems' steady interactions with their environment [KRRvW17]. A common approach, in current research and in industry, is to describe embedded systems and their real-world interactions as component and connector models [Rin14, Hab16, BS12, MT10, CGL<sup>+</sup>03]. Component and connector models describe the logical architecture of cyber-physical systems by focusing on software features and their logical communications [KRRvW17, Rin14]. In component and connector (C&C) models, hierarchical decomposed components encapsulate software features, and connectors model the data flow between components via typed ports [HRR12, The18k, DvdHT01, Mod05, Nat98, FMS11]. As extra-functional properties, e.g., worst-case-execution-time, memory and power/fuel consumption, safety, and security, are also key features for the success of embedded systems, component and connector models are often enriched with many of these properties [MRRvW16, Gru07, SSCC09, SCS11a, SSCS16, CM78, Rom85, RM06].

But, the process to develop, understand, validate, and maintain large component and connector models (with extra-functional properties) for complex embedded software is onerous, time and cost intensive [BMR<sup>+</sup>17a].

Hence, the aim of this thesis is to support the automotive software engineer (cf. Chapter 2) with:

- (i) automatic consistency checks of large C&C models,

- (ii) automatic verification of C&C models against design decisions,

- (iii) tracing and navigating between design and implementation models,

- (iv) finding structural inconsistencies during model evolution,

- (v) presenting a flexible approach to define different extra-functional properties for C&C models, and

- (vi) providing a declarative specification framework to formalize constraints on C&C models for extra-functional properties in order to execute automatic consistency checks.

The remainder of this chapter is structured as follows: Section 1.1 introduces the context of and some preliminaries for this thesis; i.e., component and connector models and their views for specifying design decisions; model based (systems) engineering and domain specific languages; and *MontiCore*, a tool for creating domain specific languages, used to engineer the language family presented in this thesis. Section 1.2 presents the requirements on this PhD thesis; these are based on the working packages of the proposal of the GIF grant I-1235-407.6/2014, that founded

the research leading to these results. Section 1.3 states the research question and describes main contributions of this thesis. Section 1.4 outlines the chapter structure of this document. Finally, Section 1.5 gives an overview of related publications created in context of this thesis.

### 1.1. Context and Foundations

The foundations for the developed methodologies, concepts, algorithms, and tools are mostly formed by previous research of Software Engineering at RWTH Aachen University in Germany and School of Computer Science at Tel Aviv University in Israel.

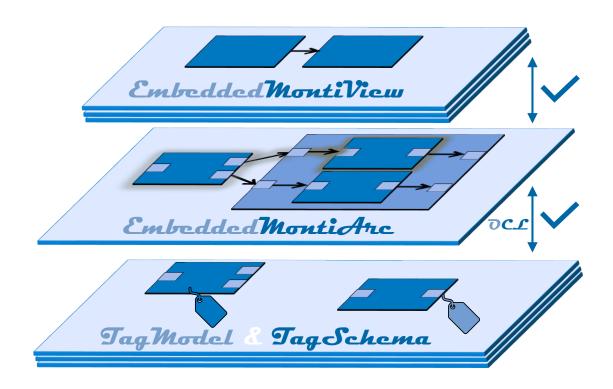

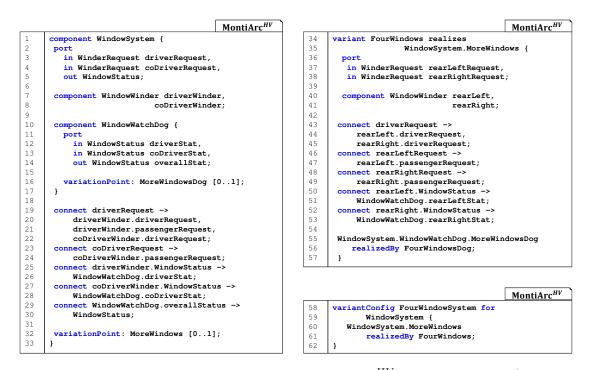

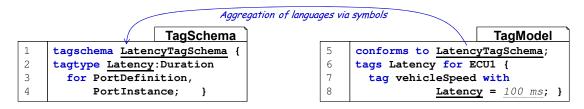

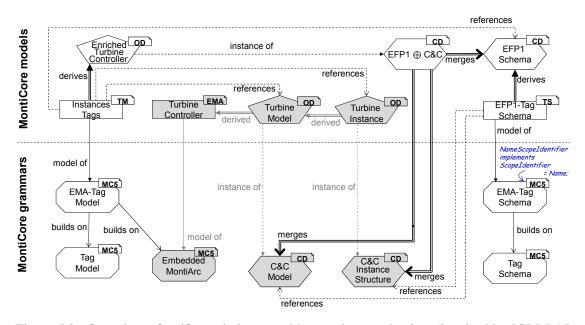

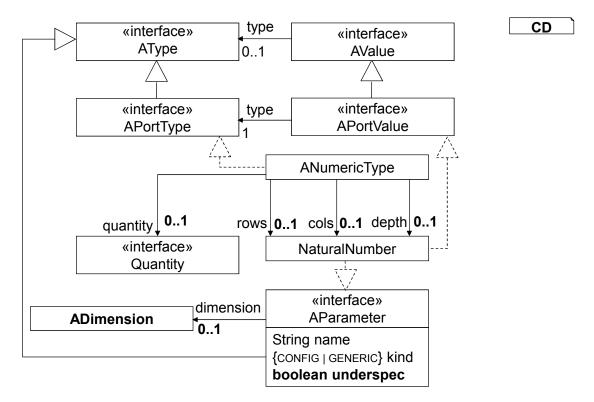

In more detail, the *EmbeddedMontiArc* language family to model and simulate cyber-physical and embedded systems is based on *MontiArc* [HRR12, Rin14, Wor16, Hab16], whereby the brain domain specific language *NestML* [Plo18, BEP<sup>+</sup>18] inspired the unit concept used in *Embedded-MontiArc*. The *EmbeddedMontiView* language, to specify component and connector design decisions, uses concepts of the textual *MontiArc* derivate for C&C views [Rin14, MRR13, MRR14]. The symbol table based tagging mechanism, presented in this thesis to enrich component and connector models with extra-functional properties, is an extension of the tagging mechanism for DSLs (domain specific languages) [GLRR15, Loo17]. The object constraint language to formalize the semantic relationship of extra-functional properties between *EmbeddedMontiArc* and *EmbeddedMontiView* models added units and advanced type resolving features to the existing UML/P *OCL* language [Rum16].

The algorithms of C&C views verification as well as the representation of positive satisfaction and negative non-satisfaction witnesses are based on previous work [Rin14, MRR13, MRR14]; this thesis adapted and extended these previous algorithms and witnesses to fit better in the area of embedded and cyber-physical systems.

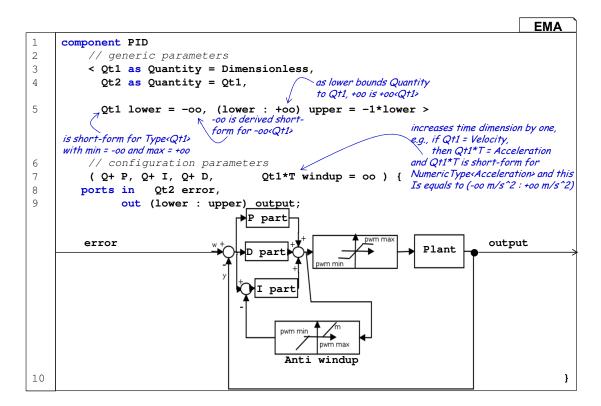

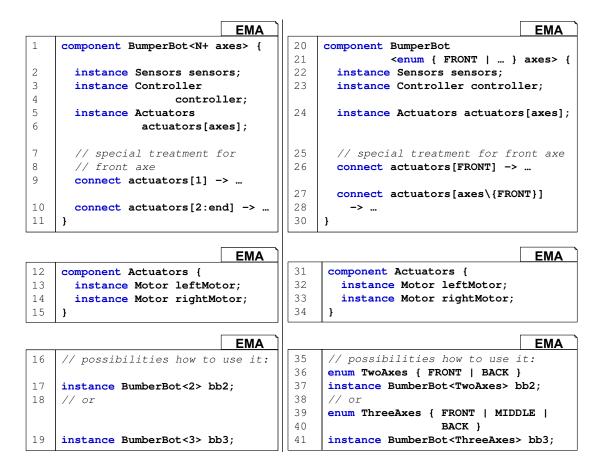

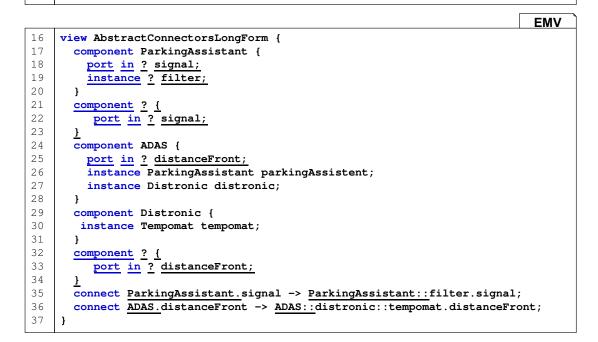

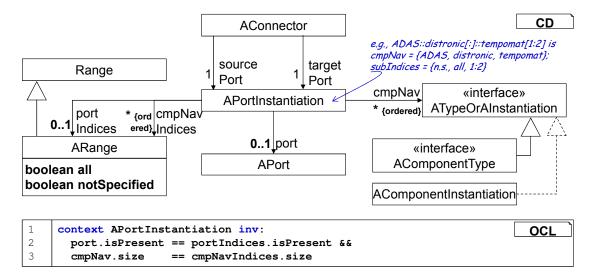

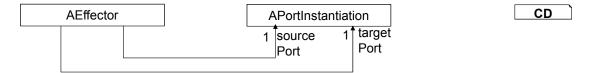

The architectural modeling concepts, esp. C&C models and C&C views, of Haber, Maoz, Ringert, and Rumpe are general and domain agnostic. This thesis extends their work with modeling concepts used very much in embedded systems; esp. new port type system with units, matrices, and ranges; static typed arrays of components and ports; as well as component interfaces for product-lines. *EmbeddedMontiArc* and *EmbeddedMontiView*, developed during this PhD thesis, introduce many new language features to facilitate an easier integration of C&C modeling concepts into current development processes of automotive<sup>1</sup> companies. To show the benefits of both languages, this thesis presents many code snippets based on real-world examples in the area of embedded systems.

The next subsections explain in more detail:

- How do component and connector models and views look like?

- What is model based (systems) engineering in the context of this thesis?

- What are the important aspects of designing domain specific languages?

- How does MontiCore help to create domain specific languages in an efficient and easy way?

<sup>&</sup>lt;sup>1</sup>Most likely, the findings of *EmbeddedMontiArc* and *EmbeddedMontiView* according to the development process of automotive systems engineering can also be transferred to other embedded system's domains, e.g., aerospace or robotics. However, this thesis evaluated these two languages according to development processes and examples provided by automotive companies (cf. Section 2.1, Section 2.2, and Chapter 8).

#### 1.1.1. Component and Connector Models and their Specification Language

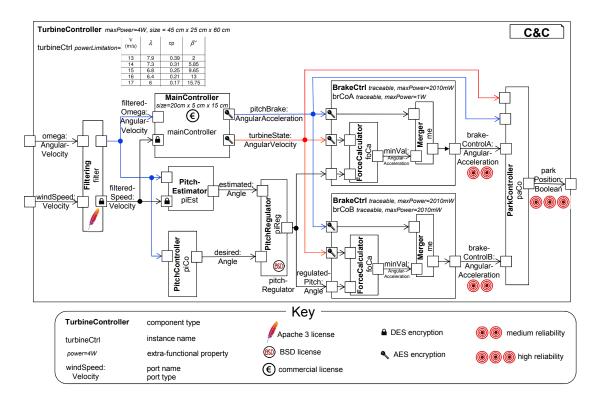

Main sources: [MR13, Section 1], [KRRvW17, Section 1], [BMR<sup>+</sup>17a, Section II]

Model-based (systems) engineering together with domain-specific languages (cf. Subsection 1.1.3) help to address the problem-implementation gap by providing a language focusing on the domain rather than on the solution. This subsection describes component and connector (C&C) models and C&C views, which are two DSLs for the logical layer used in component-based software engineering. Today, C&C models are mostly used in embedded or cyber-physical systems, e.g., in avionics, robotics, railway, (production) industry, and automotive. Typical applications developed with C&C models in automotive industry are, among others, trajectory planning, lane correction, battery management, engine control, clutch lock-up, anti-lock braking system, transmission system, automotive suspension, climate control system, power window control, electronic stability control, electronic power steering, adaptive cruise control, adaptive forward lighting, and automatic park assistance systems [KRRvW17, The18j, BMR<sup>+</sup>17a].

As the name component and connector model suggests, the structure of a C&C model consists of components at different containment levels and connectors connecting components via their typed input and output ports [MR13, Hab16, HRR12, KRRvW17, MRR13, MRR14, MRRvW16, MMR<sup>+</sup>17, BMR<sup>+</sup>17a]. Due to the many applications for C&C models, there exist already several tools and methodologies for creating, analyzing, maintaining, and synthesizing them [MR13, KRRvW17], in industry and academia; e.g., MathWork *Simulink* [The18k], *Acme-Studio* [SG04], *AutoFOCUS* [AVT<sup>+</sup>15], IBM *Rational Rhapsody Architect* [IBM18], *Modelica* [Mod05, EMO99], *MARTE* [OMG11], *LabView* [Nat98], *SysADL* [OLB16], *GALS* [MVF00] (Globally Asynchronous, Locally Synchronous), and *ASCET* [DSW<sup>+</sup>03] (Advanced Simulation and Control Engineering Tool).

The main advantage of C&C models is their hierarchical decomposition, which enables decomposing complex functions in smaller ones. This way large systems can be implemented by different teams or even different stakeholders in a divide and conquer manner [KRRvW17].

However, the strict hierarchical decomposition of C&C models (showing only one layer at a time) limits the overall design process of a system where different groups or stakeholders participate by providing partial knowledge about the system [MR13]. In contrast to the implementation process that is based on an existing architecture, the design process to create this architecture focuses on multiple user stories, or requirements. Therefore, the design process needs to deal with concern-specific interests resulting in models crosscutting hierarchical boundaries [MR13, Rin14, MRR13].

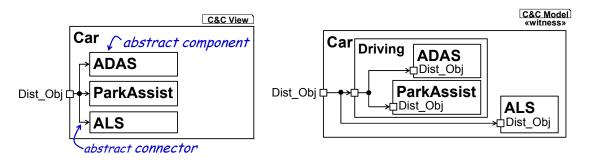

C&C views - introduced by Rumpe, Ringert, and Maoz [MRR13, MRR14, Rin14] - are invented to describe (abstract) relations between components ignoring hierarchical boundaries. Since C&C views' syntax is an extension of the well-known syntax of C&C models, C&C views describe structural properties of C&C models in an intuitive and formal way [MRR13, BMR<sup>+</sup>17a]. C&C views enable to abstract from direct hierarchy, direct connectivity, port names and types [MR13, MRR13, BMR<sup>+</sup>17a, Rin14]. The abstraction of direct hierarchy enables to omit intermediate components in C&C views. The abstraction of direct connectivity enables to connect components in C&C views which are only indirect connected in the C&C model.

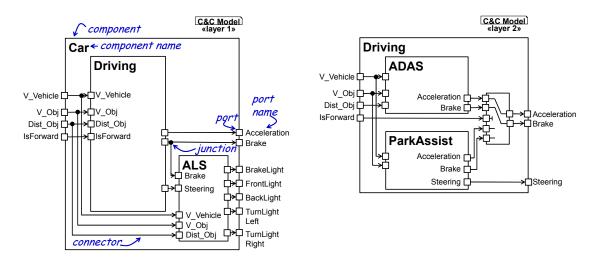

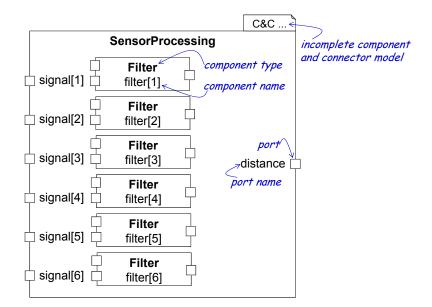

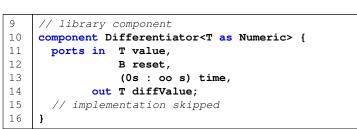

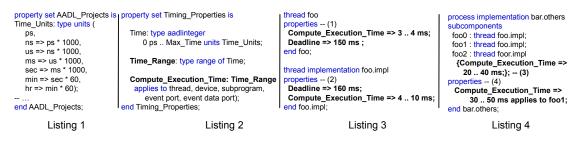

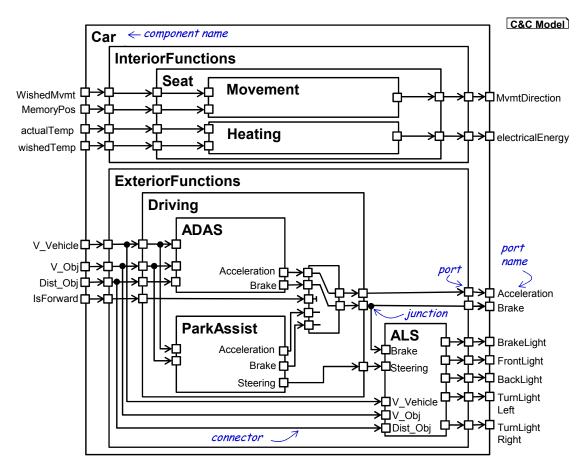

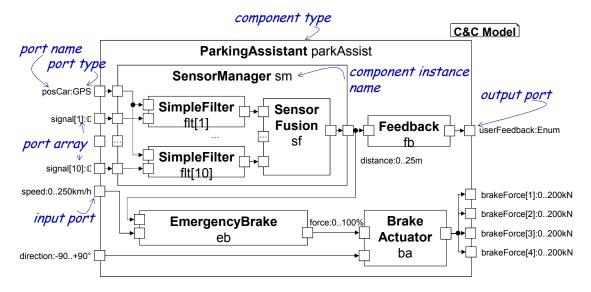

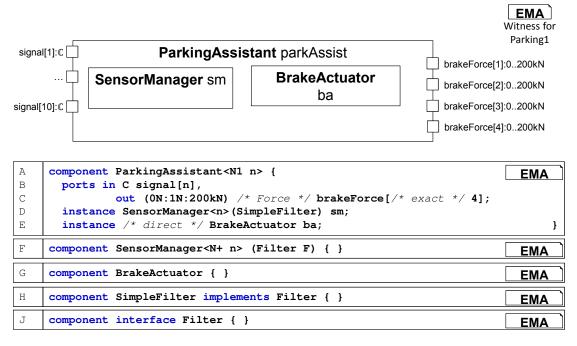

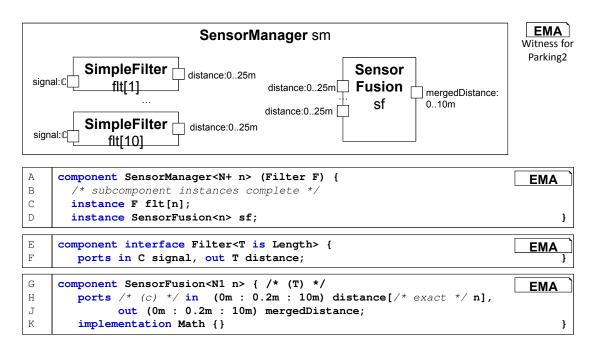

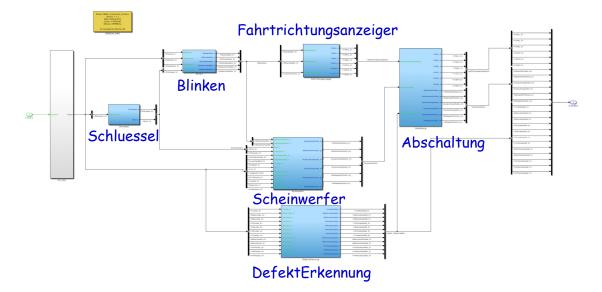

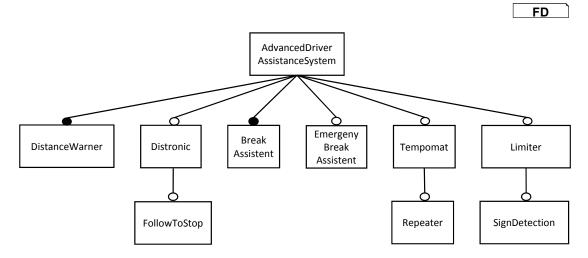

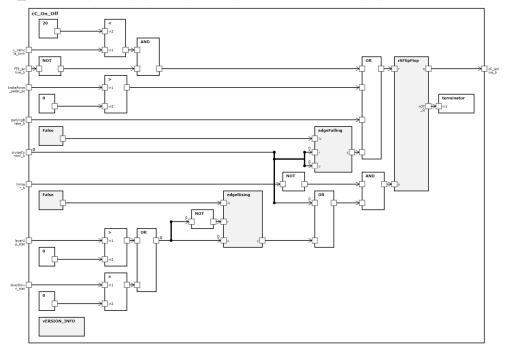

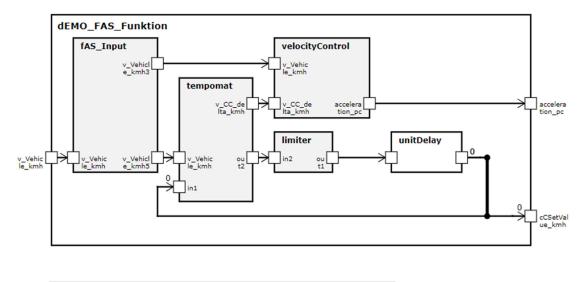

Figure 1.1.: C&C Model of a simple car software (inspired by [BMR<sup>+</sup>17a]).

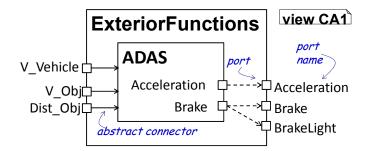

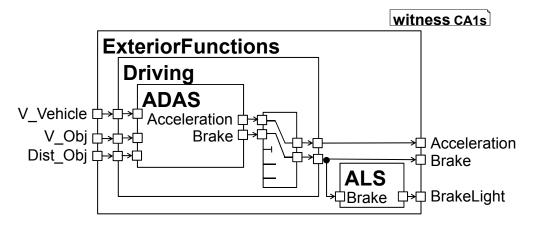

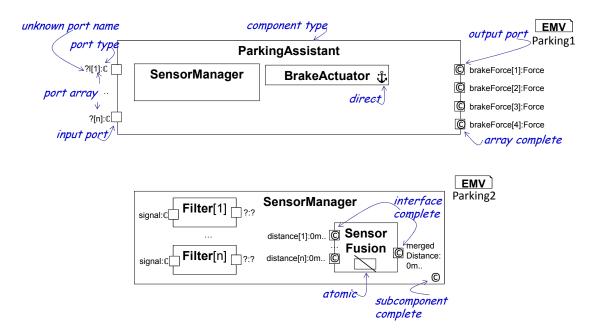

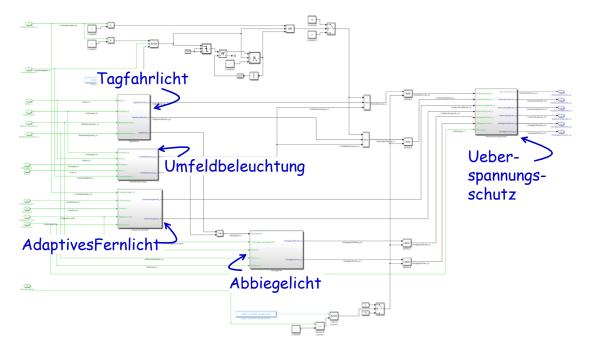

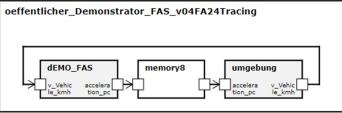

Figure 1.2.: C&C view (left) and C&C witness (right) generated based on C&C model in Figure 1.1 and C&C View (inspired by [BMR<sup>+</sup>17a]).

Specifically, a C&C view should focus on the design decision relating to one concern, user story, or requirement; and thus, a C&C view typically contains only a small subset of components and connectors belonging to a system.

Recent work [MRR13, Rin14] on C&C views already investigated (1) on C&C view synthesis to create the complete structural C&C model based on multiple structural design decisions; as well as (2) on C&C view verification to create satisfaction and non-satisfaction witnesses explaining why an implementation is (not) conform to a design decision.

The next paragraphs present the difference and the relationship between C&C models and C&C views on small examples.

Figure 1.1 shows an example C&C model of a simplified car software component. Similar to all existing C&C modeling tools, the figure shows two separate hierarchy levels. The Car component (left part in Figure 1.1) controls acceleration, brake, and light signals of a car based on the current velocity and drive direction (isForwad) of the vehicle as well as based on the distance and speed of an obstacle in front of the car. To handle these tasks, the Car component is decomposed into the Driving and ALS (Adaptive Light System) subcomponents. Since the

#### 1.1. Context and Foundations

Driving component (right part in Figure 1.1) is responsible for parking and a superior driver experience on highways; it is further decomposed into three components: ADAS (Advanced Driver Assistance System), ParkAssist, and a *Switch* merging signals.

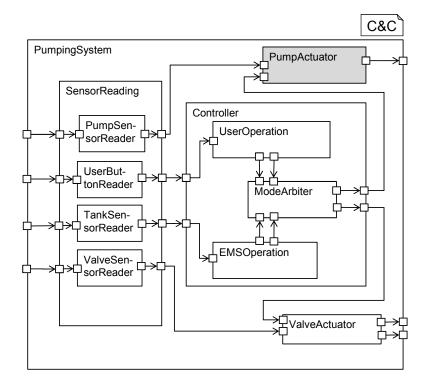

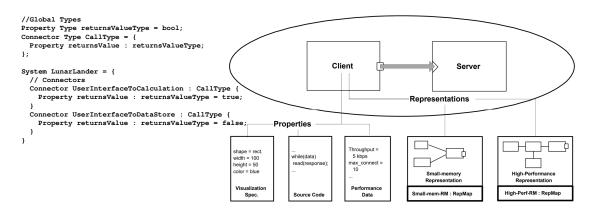

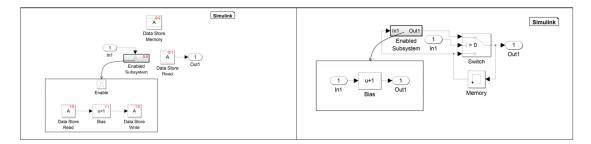

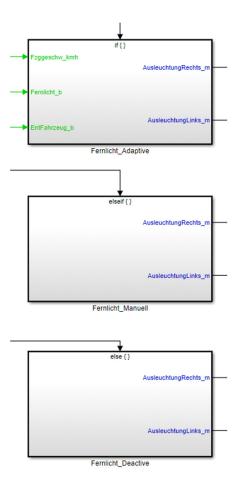

The C&C view in Figure 1.2 represents the architectural design decisions dealing with sensor data measuring the distance to the obstacle in front of the car. The C&C view states that the input port Dist\_Obj has impact on ADAS (car needs to hold distance), ParkAssist (car must fit in the parking slot), and ALS (car should not blind pedestrians) subcomponents. The crosscutting nature of C&C views enables to connect the input port with components being defined in two hierarchical different layers (cf. left and right part of Figure 1.1). Due to the hierarchical abstraction of C&C views, the left part in Figure 1.2 omits the Driving component.

The C&C witness, right part in Figure 1.2, reasons why the C&C model in Figure 1.1 satisfies the C&C View, left part in Figure 1.2. The witness contains the complete hierarchy, regarding to the C&C model, of components being addressed in the C&C view; thus, the witness contains the Driving component. Additionally, the witness contains all ports of the C&C model being addressed in the C&C view directly or being necessary for resolving an abstract connector in a C&C view to a connector chain in a C&C model. Therefore, the witness contains the Dist\_Obj port for the components Car, Driving, ADAS, ParkAssist, and ALS. The C&C view's abstract connectors: (1) connector from Car's Dist\_Obj to Driving's Dist\_Obj, and (2) connector from Driving's Dist\_Obj to ADAS's Dist\_Obj. As a result, the witness shows these two connectors; similar holds for the other connectors shown in the C&C witness.

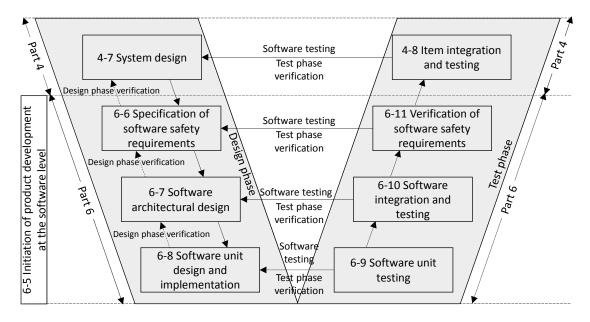

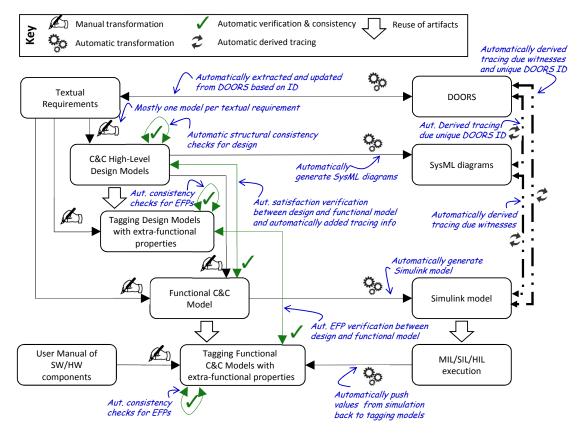

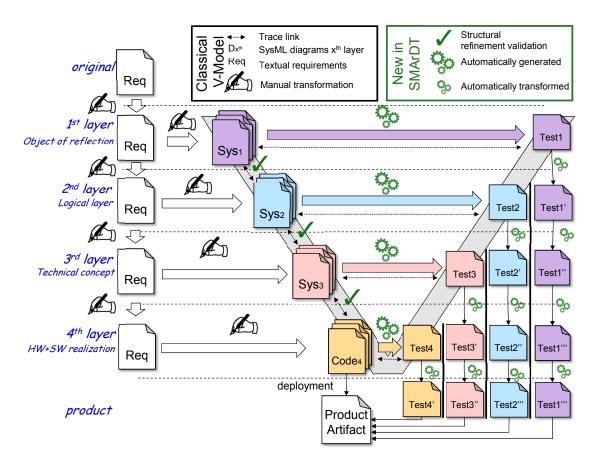

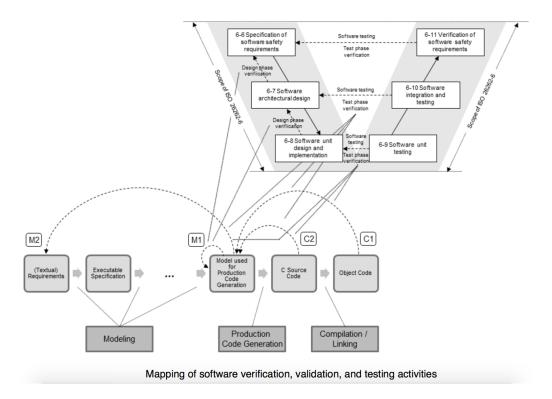

#### 1.1.2. Model Based Systems Engineering

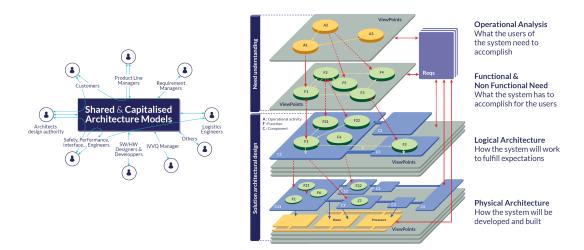

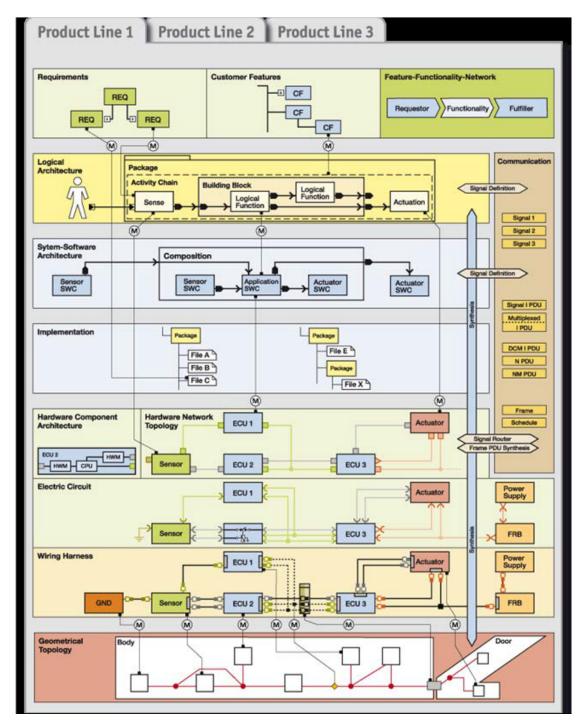

Main sources: [HR17, Section 1.1], [MSN17, Section 2.1], [CBCR15, Section 2]

Model based (systems) engineering uses models to speed up the overall software (systems) engineering process. This thesis uses the following definition for a model:

"A **model** is an abstraction of a (real) [software] system allowing predictions or inferences to be made." [Küh06]

This means a model abstracts unnecessary details [Rum16] from the original by showing specific, for the system or application interesting, viewpoints/aspects [MSN17] (cf. [Küh06, Sta73, HBB<sup>+</sup>94, BG01, Sei03, Sch12]).

There exists several development processes using models in different intensities. These processes are called **MBE** (model-based engineering), **MDE** (model-driven engineering), and **MDD** (model-driven development). Now, these processes are put into a relationship to see how they differently work with models.

MBE is a softer version of MDE; since in MBE software models play an important role (e.g., models as documentation on which developers create manually code), but they may not be first-level artifacts of the process (i.e., they may not "drive" the engineering process) [Cab14].

"Model-driven development is simply the notion that we can construct a model of a system that we can then transform into the real thing." [MCF03]. MDD uses models as first-level artifacts of the development process to generate source code, or to synthesize a larger artifact based on many smaller first-level models.

Examples of MDD at the Software Engineering chair at RWTH Aachen University are:

- MontiCore [HR17]: It uses grammar models to generate parser, visitor, and AST.

- *MontiDEx* [Rot17]: It generates a GUI and CRUDS (create, read, update, delete, and search) application logic based on class diagram models. Similar applications are MaCoCo [ANV<sup>+</sup>18], MontiWIS [Gül14], and WebDEx [Rei16].

- *NESTML* [Plo18, BEP<sup>+</sup>18]: It uses *NESTML* models to generate C++ code for the *NEST* (Neural Simulation Tool) [GD07] infrastructure. This C++ code is used to simulate neural activities in the brain.

- *MontiArcAutomaton* [Wor16]: It uses component and connector models (similar to *SysML*'s internal block diagrams) and automata as primary modeling artifacts to generate Java or Python source code.

- Facility Models [KLPR12]: They describe the energy flow inside buildings, so that positions and states of hot water circuits and central air conditions can be optimized to develop energy efficient buildings.

- Besides only generating code based on models, model artifacts are also used to synthesize one complete behavior model based on multiple LTL [MR15] or automata [Rin14] specification models. Another example for model-based synthesis is the creation of timetables for TV channels based on broadcast license permissions for movies, or series.

MDE is more general than MDD, since development is only one activity within engineering. Activities of MDE, which are not part of MDD, are, e.g., model-based evolution [RSvW<sup>+</sup>15, KSRvW18], variability modeling or extraction [KRR<sup>+</sup>16, RRS<sup>+</sup>16, HRR<sup>+</sup>11], and maintaining legacy systems [BRR<sup>+</sup>10]. Thus, the relationship (based on Jordi Cabot's blog [Cab14]) can be summarized as follows: MBE  $\supset$  MDE  $\supset$  MDD

In the following this section continues to explain the wordings MBSE, CBSE, and DSL.

**MBSE** (model-based systems engineering) uses models to describe system requirements and system designs as well as support system analysis, and system validation [INC07]. In contrast to model-driven software engineering - mostly focusing on one domain such as financial service systems, insurances, or web applications - system engineering is mostly based on multiple domains - e.g., engineering a car deals with the following domains: embedded software, mechanical, electrical, and safety. The production process to create the system also has influence on the system itself (e.g., the price, or the amount of systems that can be produced). Therefore, model-based production [BKL<sup>+</sup>18] also belongs to model-based systems engineering. Models, with their cross-cutting nature helps to express relations between different domains in systems engineering.

**CBSE** (component-based software engineering) is a development paradigm by assembling large software systems from components [Nin97]. One well-known concept to model structural relationships between components in CBSE are C&C models (cf. Subsection 1.1.1). C&C models such as *SysML* IBDs (internal-block diagrams) or *SysML* BDDs (block-definition diagrams) are often used to design the logical layer of embedded software in a systems engineering context.

**DSLs** (domain-specific languages) are modeling languages formalizing the application structure, behavior, and requirements within a particular domain [Sch06]. DSLs tackle the problemimplementation gap [FR07] - i.e., the conventional gap between the domain problem and the

#### 1.1. Context and Foundations

GPL (general purpose language, e.g., C++, Java, or Swift) based implementation - leading to accidental complexity [CCF<sup>+</sup>15].

Well-known examples for DSLs, their extensions, and their interaction delivers the world wide web consortium (W3C) as they defined for each problem (webpage structure, layout, graphics, math expressions, or action handling) its own language such as HTML [W3C17b], CSS [W3C17a], SVG [W3C11], MathML [W3C14], JavaScript/ECMAScript [ecm18]; and also extend the HTML language with new keywords for addressing new problems (e.g., Payment API [W3C18b], or HTML Media Capture [W3C18a]).

In contrast to GPLs - mostly programming languages of level 3 - executable DSLs are programming languages of level 4 [HM02, VDKV00] or level 5 (AI-based DSLs [Gri84]), because DSLs provide much higher abstractions due to their tailored problem-specific (and mostly declarative) nature. But not every DSL is executable, e.g., SVG DSL for vector graphics.

DSLs include the following features: concrete syntax, abstract syntax, context conditions (also called static semantics), and (dynamic) semantics (also called meaning) [HR00, HR04]. The **concrete syntax** determines the representation of a DSL. The concrete syntax is the representation how the user of the DSL needs to write down its concrete models. The concrete syntax of a DSL should be as close as possible to existing notations used by domain experts [KKP<sup>+</sup>09]. The concrete syntax of a tool can be textual or graphical (also includes table-based like Excel) [GKR<sup>+</sup>07, KKP<sup>+</sup>09].

DSLs for textual languages mostly use parser generators such as *ANTLR* [Par13], *Yapp* [MMY10], *Rats!* [Gri06], *PEG.js* [Kur16], *Waxeye* [OVM15], or *Mouse* [Red09] to produce parsers for transforming text into a traversable internal data structure.

Graphical tooling such as *MPS* [PSV13], *Gemoc* [BDV<sup>+</sup>16], or *MetaEdit*+ [TR03] are always projectional editors [VS10]. Thus, these tools modify directly the underlying internal structure, avoiding the parsing step, and so they do not need to deal with "token clashes". The concrete syntax of graphical models are the used graphical elements such as lines, arrows, boxes, stroke width, or color.

The **abstract syntax** of a language describes its essential structure; the abstract syntax does not contain semantically irrelevant words [CBCR15], which make only the concrete syntax better readable. The *ANTLR* parse tree [Par13], the internal structure created by the parser, is not an abstract syntax of a language, because the parse tree contains the complete syntactic sugar of the textual input file. Some tools, e.g., EMF (Eclipse Modeling Framework) [SBMP08], enable to define directly the abstract syntax of a language without using any concrete syntax.

The tree structure after parsing textual input and removing irrelevant concrete sugar is often called abstract syntax tree (AST). This thesis uses the notation of abstract syntax based on Nazari [MSN17]: "the abstract syntax consists of both the AST and the symbol table" (symbol table is introduced in Subsection 1.1.3).

**Context conditions**, sometimes also called static semantics, are Boolean predicates over the abstract syntax of a DSL [HR00, CBCR15]. Context conditions only constraint the syntax; they do not describe the semantic domain, the meaning of the syntax [HR04]. For example, the concrete syntax 10 + 11 can be interpreted as 21 when applying the semantic domain of natural numbers; or as 01 when applying the Boolean algebra domain with + as *exclusive-or* operator.

Typical context conditions of DSLs are resolving declarations and type checking [Edw00, Car96, Bag10]; e.g., variables must be declared before referenced, a file contains at most one public class in Java, or the type of an assignment's left side must be compatible to the type of the right side. Context conditions can also be used to detect code smells violating conventions, e.g., Java classes should start with a capital letter [Ora99]. A model is well-formed if it fulfills all context conditions [CBCR15, MSN17].

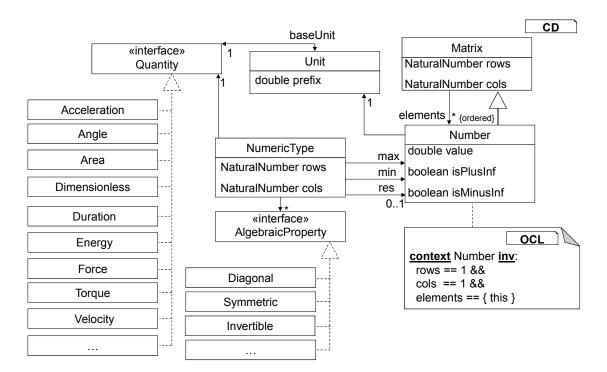

A language's **type system** is mostly part of the essential structure (abstract syntax) and of a language's context conditions. DSLs with a behavior model, e.g., some kind of expression language, mostly define a type system [JSH13]. The type system has inference rules for deriving the type of a composed expression term based on the types of single operators. A type system also has context conditions which check whether an expression based on the (inferred) type information is valid. The type system of a DSL should reflect the problem domain.

For example, a DSL for matrices similar to *MATLAB* can have a matrix-based type system containing matrix dimensions and algebraic matrix properties: One type inference rule is, e.g., how to calculate the matrix dimension after a matrix multiplication. One constraint is, e.g., that matrix addition forces that matrix dimensions of the left and right side are equal.

A type system for an English-like DSL could be based on grammar rules such as singular and plural: An inference rule could be that a list (comma separated, or just with an and or or) of singular nouns is the same as a plural noun. A constraint could be that after a plural noun no singular verb is allowed (Evgeny and Michael programs Java is wrong).

For *xText* [EB10] and its expression framework *Xbase* [EEK<sup>+</sup>12] exist *XTS* [Voe11], *Xsemantics* [Bet13], and *TS4DSL* [JSH13] as tools for type declaration, type inference, and type checking.

The semantics of a language provides the meaning, in a well-defined and well-understood domain, of each well-formed syntactical element. There are three kinds how to define the semantic of a DSL:

- Denotational semantics: It defines a function mapping of the concrete or abstract syntax to a mathematical domain, e.g., set theory by Scott and Strachey [Ten76, SS76].

- Axiomatic semantics: It defines the semantics and proofs the correctness by using axioms [Hoa69].

- Operational semantics [TP97]: It maps the concrete syntax of a DSL directly to code of a real (or simulated) machine. The weakness is that the machine (simulated, virtual, or real hardware) needs a clear semantic description [Edw00].

*EmbeddedMontiArc*'s semantic is denotational as its syntax is mapped to I/O-EFA (input/output extended finite automata) structures by using the same semantic as *Simulink* models with fixed-step size solvers [RSvW<sup>+</sup>15]. Later in Chapter 7 this thesis uses denotational semantics to map the meaning of *EmbeddedMontiView* to Boolean mathematical predicates about *EmbeddedMontiArc* models. *OCL/P*'s semantic is operational; its meaning is defined by mapping it to Java code [Rum16, Section 5.3] and the meaning of Java code is defined by its byte code and the Java Virtual Machine [HBL99, Pus98].

#### 1.1. Context and Foundations

#### 1.1.3. MontiCore

Main sources: [HR17, Section 1.1, Section 4.2], [MSN17, Subsection 2.2.2, Section 3.8, Section 8.1]

Subsection 1.1.2 shows that models and model-based (systems) engineering are used in many domains, e.g., to speed up development, improve quality, and reduce maintainability costs. A language workbench is a tool to create efficiently new DSLs [Fow10, Gho10, VBD<sup>+</sup>13, MSN17, Rot17]. With *xText*, *MPS*, *Enso*, *Mas*, *SugarJ*, *Whole Platform*, *MetaEdit+*, *Onion*, *Spoofax*, *Rascal*, and *MontiCore* exist already a number of language workbenches for agile language engineering [PPL14, EVDSV<sup>+</sup>13]. In contrast to most other existing language workbenches, *MontiCore* is a light-weight, highly customizable, and functional oriented language workbench framework [GKR<sup>+</sup>08, KRV08, Kra10, KRV10, Völ11, Sch12, Hab16, Rei16, Loo17, MSN17, Rot17, HR17].

MontiCore's main features are [HR17]:

- Modular definition of languages

- Easy definition of large language families via:

- Independent language development

- Language extension

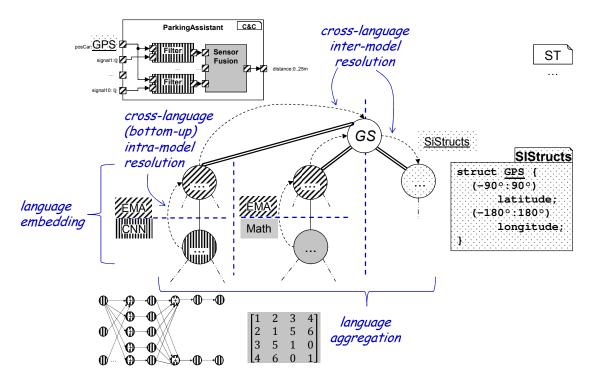

- Language embedding

- Language aggregation

- Composition of language tools

- Creation of language specific Eclipse [KRV07] and web editors [KRRvW18, Ron17]

- Assistance for model analysis

- A single source file defines concrete and abstract syntax, as well as parser and internal representation of models

Due to the more than 10-year existence of *MontiCore*, there exists a large grammar repository of many different languages belonging to many different domains, which can be reused to create your own language in a minimum amount of time.

For example, MontiCore provides languages for the following domains [HR17]:

- Basic domain: Literals, Lexicals, Numbers, Matrices, Comments, Stereotypes, and Tagging

- UML: Class, Object, Activity, and Sequence Diagrams as well as StateCharts and OCL

- SysML: Units, MontiArc (ADL), Automata, Functional nets, CNNArch, MontiMathOpt (optimization language), and Feature Diagrams as well as EmbeddedMontiArc and EmbeddedMontiView

- GPLs: Java 7, Ansi-C++, Python, and JavaScript

- Cloud: *MontiSecArc* (security), *MontiClarc* (cloud architecture), *MontiWIZ* (online formular wizard)

- Text-based: Curriculum, Right Restriction for TV movies/series

Important languages for this thesis are class diagrams, *OCL*, and *MontiArc*. Subsection 1.1.1 shortly introduces *MontiArc*.

Class diagrams are part of structural *UML* (Unified Modeling Language) diagrams. For example, class diagrams are used for object oriented modeling or for data modeling as they describe the data structure via attributes of objects and their relations via associations. Another use case for class diagrams is to describe the structure of systems, e.g., as abstraction of Java or C++ code systems, by showing only their classes with their relations (implements/extends and association relation), their attributes, as well as their methods.

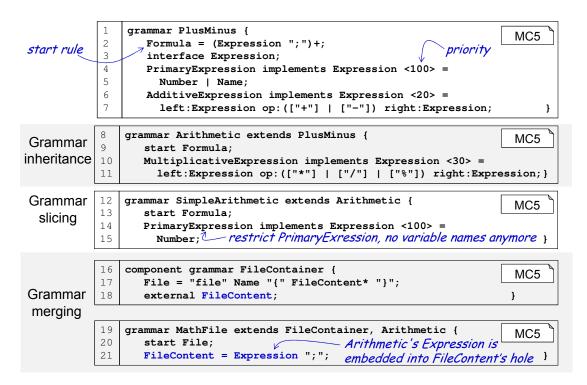

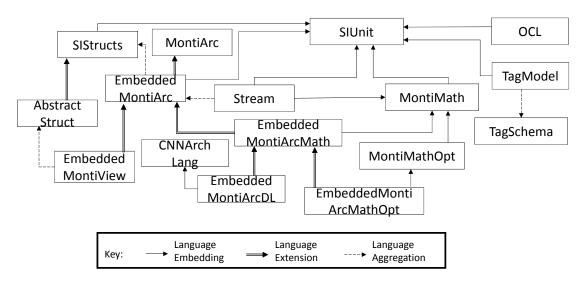

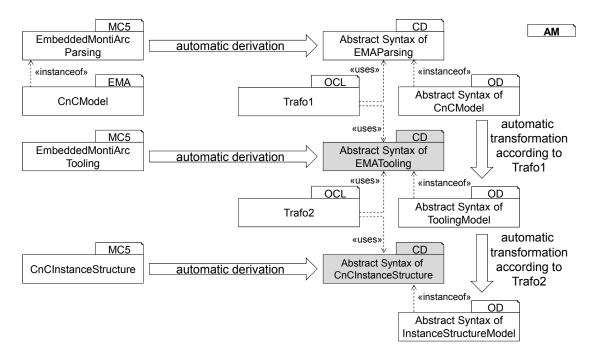

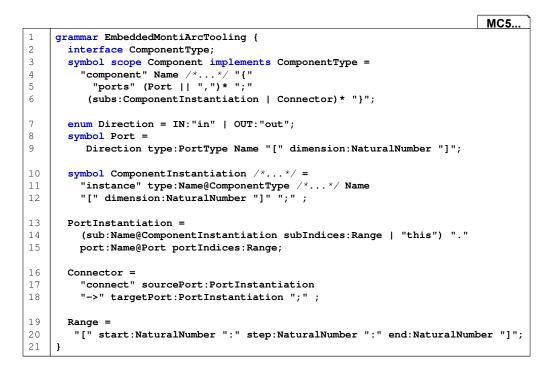

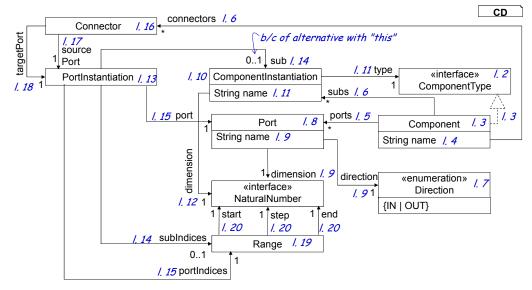

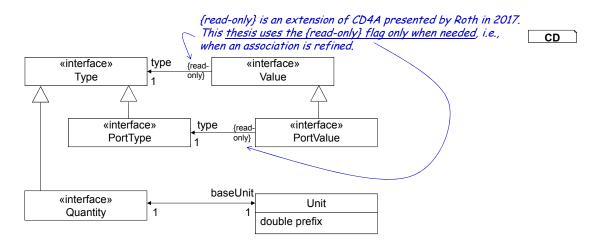

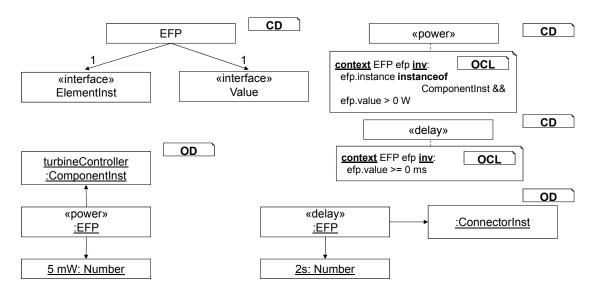

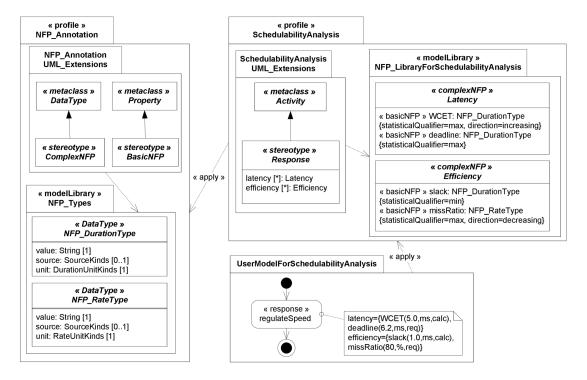

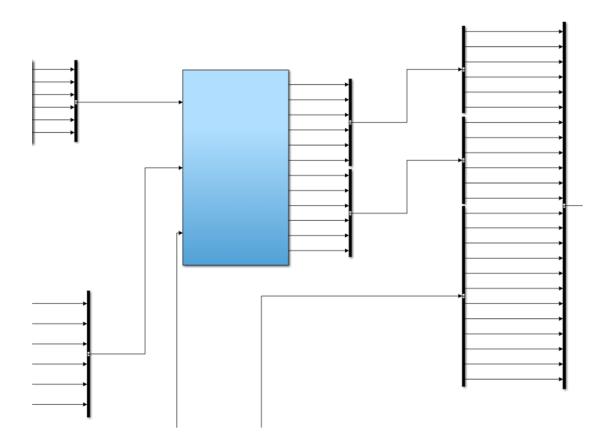

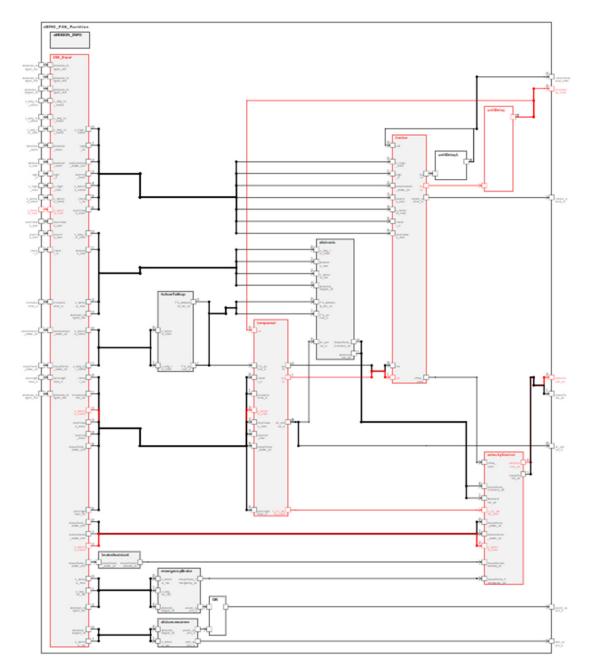

Figure 1.3.: Grammar Composition in MontiCore 5

*OCL* (Object Constraint Language) is an extension to *UML* models, e.g., class diagrams, to specify precisely detailed aspects of systems. *OCL* is typed, declarative and side-effect free [Cab12]. This thesis uses the *OCL/P* textual notation of Rumpe [Rum16] to specify *OCL* constraints. Chapter 6 explains *OCL* in detail. The paper [BRvW16] illustrates on five constraints the syntactic difference between OMG *OCL* 2.4 and *OCL/P*.

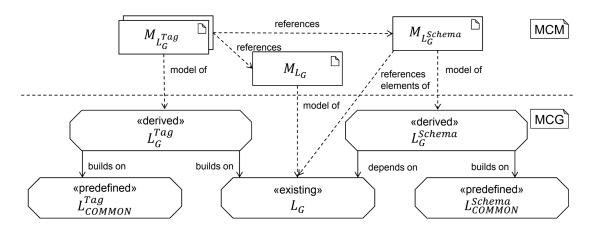

The rest of this subsection explains the concepts how to create a large language family similar to *EmbeddedMontiArc*, the C&C language family introduced in this thesis and described in the next chapters. It shows how eloquent *MontiCore* handles language inheritance, slicing, and merging via grammar files. Section 4.6 describes how the resolving mechanism in *MontiCore* helps to find declared symbols across different DSLs enabling language aggregation and embedding.

Information about the technical architecture of *MontiCore*, or how the here presented concepts of *MontiCore* are implemented, or example code snippets explaining how to use these *MontiCore* features to develop your own DSL are explained in detail in the official "*MontiCore* 5 Language Workbench" book [HR17] and in the thesis "*MontiCore*: Efficient Development of Composed Modeling Language Essentials" [MSN17].

Similar to other DSL tools, e.g., Melange [DCB<sup>+</sup>15], *MontiCore* also supports language inheritance, slicing, and merging. In contrast to Melange, which specifies these language relations via model types in the abstract syntax, *MontiCore* uses a grammar file to enable inheritance, slicing, and merging not only on the abstract syntax, but also on the concrete one.

The top listing in Figure 1.3 shows the *MontiCore* grammar for a basic expression language. This listing shows that the *MontiCore* grammar format extends EBNF (Extended Backus-Naur

#### 1.1. Context and Foundations

form) to specify productions for the lexer and the parser. As shown in lines 2, 4, 6, 10, 14, 17, and 21 most productions are assignments and consist of a left-hand side (LHS) part and a right-hand side (RHS) part.

The LHS of a rule defines a nonterminal. The RHS defines the production's body of the LHS nonterminal. The RHS may consists of any combination of lexicals, terminals, or nonterminals. The elements on the RHS may be annotated with cardinalities describing how often an element appears: ? for 0 to 1 times; + for 1 to infinite times; and  $\star$  for zero to infinite times. The pipe symbol | is used to describe alternatives.

In contrast to *ANTLR*, *MontiCore*'s extended grammar format borrows several concepts from object-oriented languages such as Java:

- (i) definition of production interfaces,

- (ii) definition of abstract productions,

- (iii) implementation of production interfaces, and

- (iv) extension of production interfaces.

Similar to object oriented languages where interfaces can be (a) marker interfaces without any further function signatures, or (b) "normal" interfaces defining a contract that all classes implementing it should follow [Die17]; *MontiCore* also supports these two kinds of interfaces for productions: (a) the first kind has no RHS meaning it does neither define any concrete nor abstract syntax; (b) the second kind has a RHS defining the signature (abstract syntax) for all nonterminals implementing it [HR17].

Line 3 defines the Expression interface. Interfaces enable to decouple the definition of languages as they create open extension points [HR17]. These open extension points enable that the Expression interface may not only be implemented in its own grammar PlusMinus, but also in the two other grammar files Arithmetic and SimpleArithmetic. Formula in line 2 uses the interface nonterminal Expression in its RHS; and thus, it includes all nonterminals implementing Expression. If no priority is explicitly defined, the occurrence order of the definitions of the implementing nonterminals is used.

If a grammar contains no start rule as shown in line 9, then the first production rule is a grammar's start rule. Therefore, valid input files regarding to the PlusMinus grammar are:

- −17;

- x1;

- -17 + B;

- 3; x1 + 5 B;

The Arithmetic grammar extends the PlusMinus grammar, and, thus, it has access to all PlusMinus's nonterminals. Additionally, the Arithmetic grammar adds a new production rule implementing the Expression interface. The Arithmetic's inherited Formula production using the PlusMinus' Expression interface includes all nonterminals of the Arithmetic and all nontermals of the PlusMinus grammars, which implement the Expression interface. Since the priority of the MultiplicativeExpression is higher than the one of the AdditiveExpression, but lower than the priority of the PrimaryExpression; the Formula rule includes first PrimaryExpression, then MultiplicativeExpression, and last AdditiveExpression.

A valid input file according to the extended  ${\tt Arithmetic},$  but an invalid input for the  ${\tt PlusMinus}$  is:

• x1 + 5 \* 3;

*MontiCore* also supports slicing grammars (removing words belonging to a language) by extending a language and overwrite an existing nonterminal to restrict some allowed words. An example is shown in lines 14 and 15 where the inherited PrimaryExpression nonterminal is overwritten to accept only numbers and no (variable) names anymore.

Grammar merging, also known as grammar embedding, combines the words defined by both grammars in a controlled way. The MathFile grammar embeds the Arithmetic's Expressions interface production into the FileContainer's File production by binding the external production Content to Expression (cf. l. 21).

The component grammar FileContainer (cf l. 16) is an incomplete grammar, and thus, cannot be used standalone. The definition of the external production FileContent (cf. l. 18) creates a slot defining a variation point: So multiple grammars can extend this FileContainer grammar and bind FileContent differently (e.g., expressions, URL links, automata, etc.).

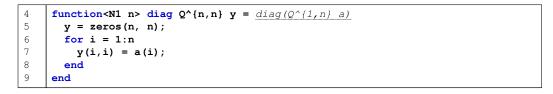

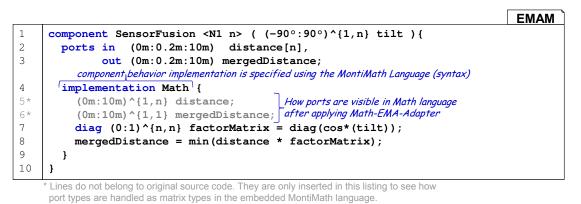

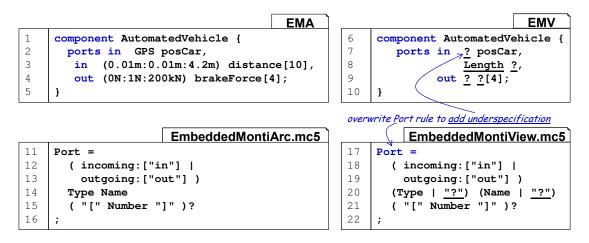

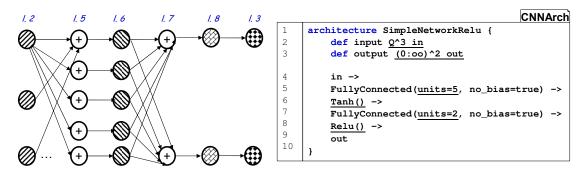

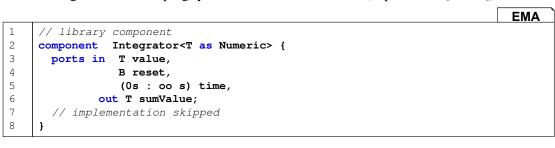

The later in this thesis presented language *EmbeddedMontiArcBehavior*, extending the pure structural C&C language *EmbeddedMontiArc* with behavior, creates a variation point for behavior to facilitate different behavior implementations: *EmbeddedMontiArcMath* has a *MATLAB*-like behavior implementation, and *EmbeddedMontiArcDeepLearning* defines the behavior of atomic components via a CNN (Convolutional Neural Network) as used in deep learning applications.

Grammar extension and the here mentioned interface mechanisms enable to engineer a large language based on smaller ones. This is one of the most valuable features of *MontiCore*. For example, *ANTLR* does not contain this feature, and so the concrete and abstract syntax of a language must be completely defined in one very large g4-file; also reuse of grammar rules (e.g., names, numbers, or expressions) can only be done via copy and paste in *ANTLR*.

The previous paragraphs shows that *MontiCore* enables to combine concrete syntax as well as ASTs of different languages in an efficient way. But as mentioned in Subsection 1.1.2 symbols belong to the abstract syntax, too. Symbols are, e.g., created when defining variables, and symbols are, e.g., used when resolving previously defined variable names. All symbols of a language family are stored in a symbol table.

According to Nazari [MSN17] is a symbol table a graph-based data structure containing of scopes, where each scope is a local repository for symbols, to fulfil the following tasks:

- (i) mapping names to symbols representing essential model information;

- (ii) organizing and finding types, declarations, implementation details, etc. of model elements in an efficient way; and

- (iii) representing the essence of a language, i.e., of its models by including model interfaces constituted by the language interface [MSN17, CBCR15].

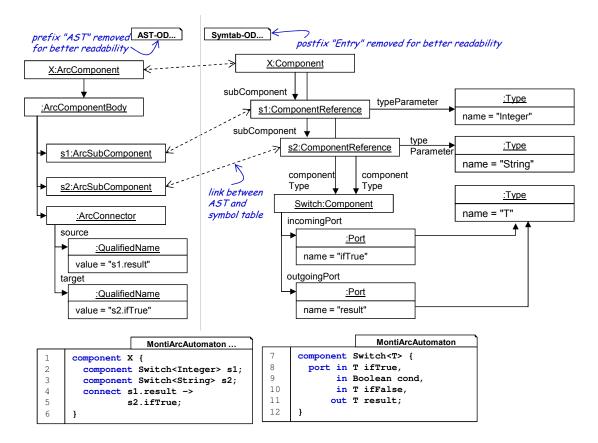

For C&C models, described in Subsection 1.1.1, the essential information is: in- and output ports (i.e., the interface) of a component, subcomponents a component is decomposed of, dataflow between ports, as well as types of ports and components. For example, the symbol table supports finding a component by its name, and then navigate efficiently through the essential data structure.

*MontiCore*'s ability to combine grammars and to exchange symbols between languages enables the development of modular language components and tools which can be completely reused to engineer large language families and powerful modeling tools.

## 1.2. Requirements on PhD Thesis

To integrate C&C architectural modeling and its C&C views verification techniques into industrial development processes of embedded and cyber-physical systems, this section summarizes the requirements on this PhD thesis in order to improve the existing C&C (views) languages *MontiArc* and *MontiArcView*.

Most results of this thesis are founded by the German Israeli Foundation (GIF Grant No: I-1235-407.6/2014) as a joint work together with Tel-Aviv University. This section contains text fragments of the corresponding proposal [MR13, Section 3].

#### 1.2.1. Enhancing the C&C Views Language

The basic C&C views language based on Maoz et. al. [MRR13] should be enhanced by integrating extensions of *AADL* [Soc06], *SysML* [FMS11, OMG15], and specific application domains such as automotive [SG07] or robotics [BKH<sup>+</sup>13].

The following extensions of C&C Views should be supported:

(R1) Component instantiation and component/connector types

Since existing architecture description languages already have an instantiation mechanism for component reuse (including types, subtypes and their well-formedness rules), C&C views should also introduce such an instantiation and typing mechanism. Furthermore, advanced language features such as parameter instantiation, or generic component types should be inspected for the C&C views concept.

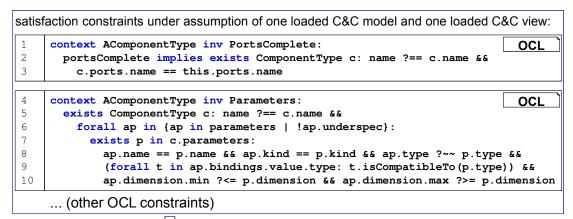

#### (R2) An associate predicate language

While C&C views are intuitive and expressive enough to specify abstraction of C&C models - e.g., by omitting complete hierarchy or ports in connections - not all structural properties of C&C models can be expressed by C&C views. Thus, an *OCL*-like constraint language with quantification support over components, connectors, and ports and related operations to its C&C views should be created. The language should be designed that its answer whether the constraint is satisfied or not is decidable; but the language should be able to constraint "the number of ports of a component" or "specify the completeness of a given component hierarchy" in a short compact form.

#### (R3) Domain-specific language adaptations and extensions

For future application of C&C views in industry, the C&C views language must support domainspecific extensions to become more friendly to engineers. Additionally, C&C views language and its corresponding C&C model language should support a way to add domain or applicationspecific properties (e.g., extra-functional properties being used in automotive industry).

#### 1.2.2. Advancing C&C Views Analyses

(**R4**) As the C&C views language is enriched by more and more features, the C&C model language and the formal satisfaction relation between C&C views and C&C models must be updated. Also introducing component types makes the verification problem much harder. In this case also parts of the already existing algorithms might be updated in order to have a good scalability up-to medium-large industry models.

(**R5**) Also a Boolean answer to the verification problem is mostly not useful enough. Therefore, esp. for negative verification results, a meaningful witness should be generated. The witness should explain the reason (or reasons) why a C&C model does (not) satisfy its C&C design view.

#### 1.2.3. Integrating C&C Views in the Development Process and Environment

Since existing development processes and their tools are all about hierarchical decomposition of systems to sub-systems, and thus, these tools represent only a single hierarchy/sub-system to the engineer at a time; these tools are not suited for the crosscutting nature of C&C views and their verification. Therefore, existing processes and tools must be adopted to take advantage of C&C views together with their abstraction mechanisms and analysis methods.

This requirement consists of the two sub-requirements:

#### (R6) New design and development processes:

Existing design and development processes based on C&C models should be investigated. Additionally, these mostly hierarchical based processes should be adapted to use C&C views; and usage scenarios for design, development, or maintenance where C&C views support the adapted process should be worked out so that the benefits of integrating C&C views with their verification into existing processes becomes obvious.

#### (R7) New modes of interaction:

Existing tools represent only one hierarchy of a system or its sub-systems. This means it is not possible to see two components and their interaction between them, if these two components are not on the same hierarchy level. Therefore, a crosscutting visualization of a view as well as a seamless navigation between C&C model and its views in both directions should be developed.

#### 1.2.4. Evaluation

(**R8**) The new enhanced C&C view language should be evaluated in an industrial context. The evaluated setting should show the benefits and weaknesses of the C&C view approach integrated into existing processes. The evaluation together with an industrial partner should show how efficient this approach is in the daily-life of engineers. Thereby, we will compare the results of C&C view verification against its manual verification, in terms of speed, needed human resources, and correctness.

#### 1.2.5. Further Remarks

This thesis focuses on the C&C view and the C&C model language extension, support of extra-functional properties, *OCL*-like specification language for C&C models, the extended formal satisfaction relation between C&C views and C&C models, as well as how the C&C verification can be integrated in existing development processes by adopting the current modeling methodologies. Additionally, this thesis contains results of an industrial case study together with Daimler AG about C&C views and their verification.

This thesis neither contains C&C views synthesis nor C&C views refinement.

### 1.3. Objective and Main Results

The following research question summarizes the main research goal of this thesis:

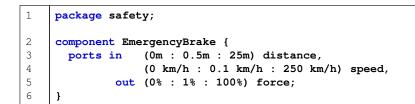

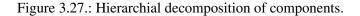

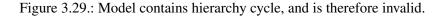

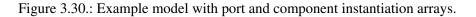

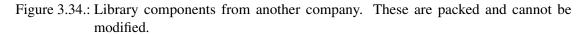

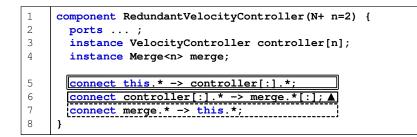

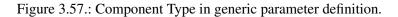

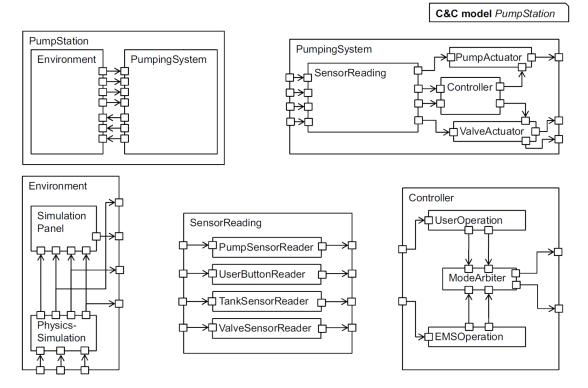

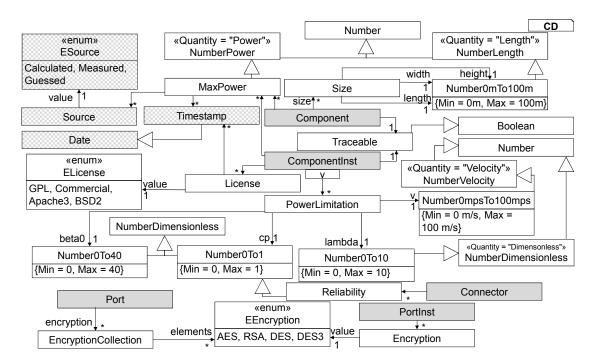

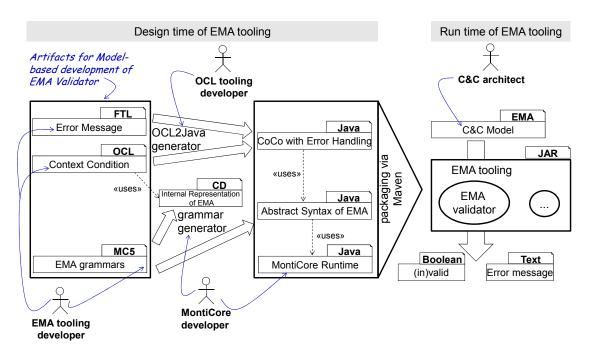

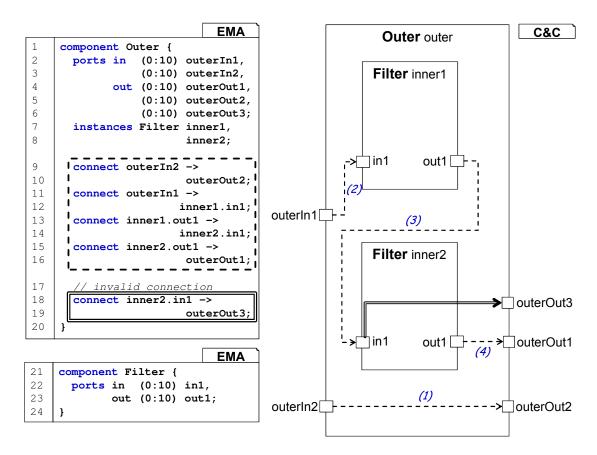

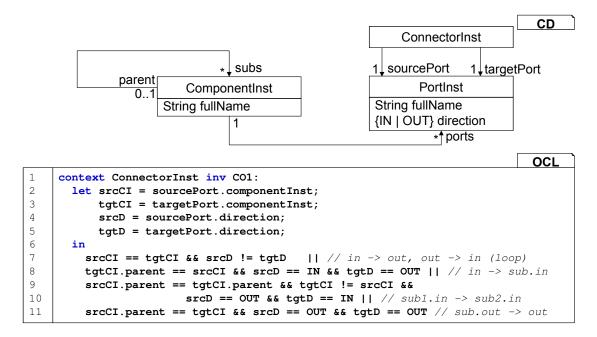

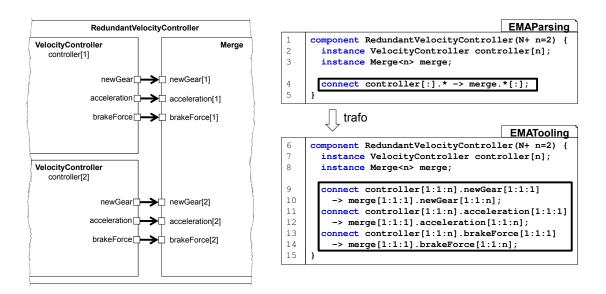

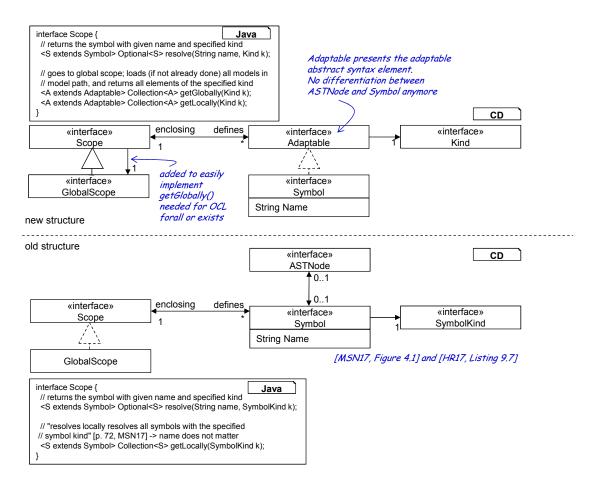

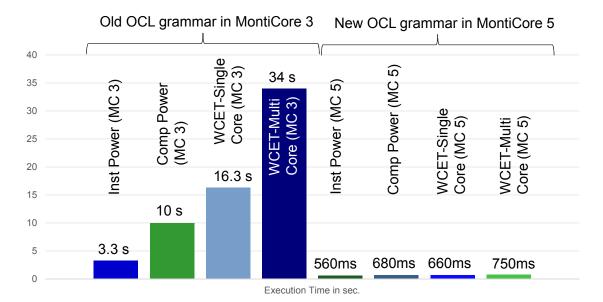

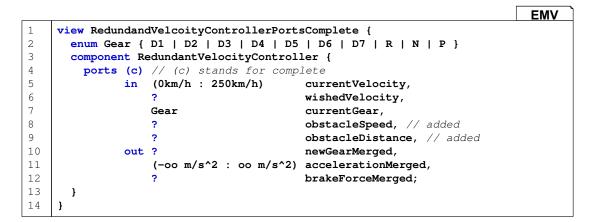

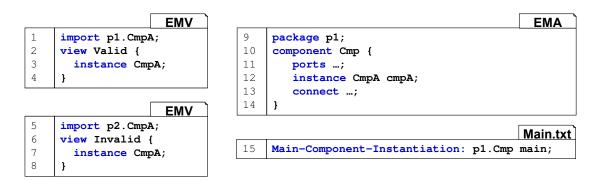

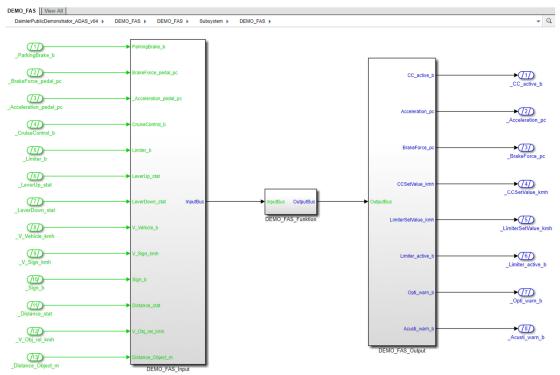

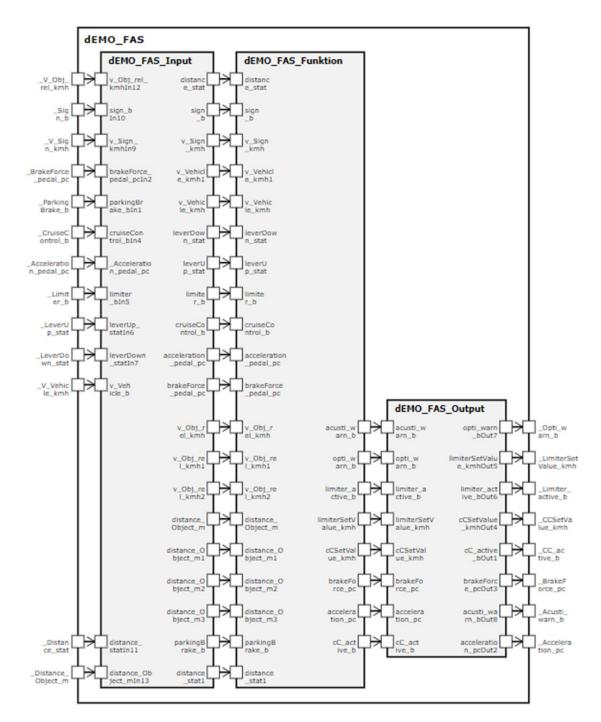

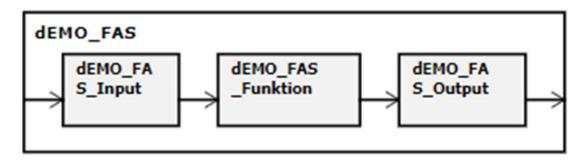

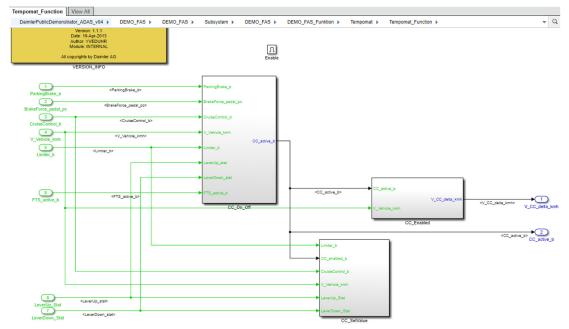

How can domain specific languages support the software systems engineering process for cyber-physical systems by defining structural design decisions and extra-functional properties in an efficient, agile, and intuitive, but also unique and formal way so that industrial-size component and connector models can be validated against them?